| ARM DDI 0029E       | ω Ν ¬                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

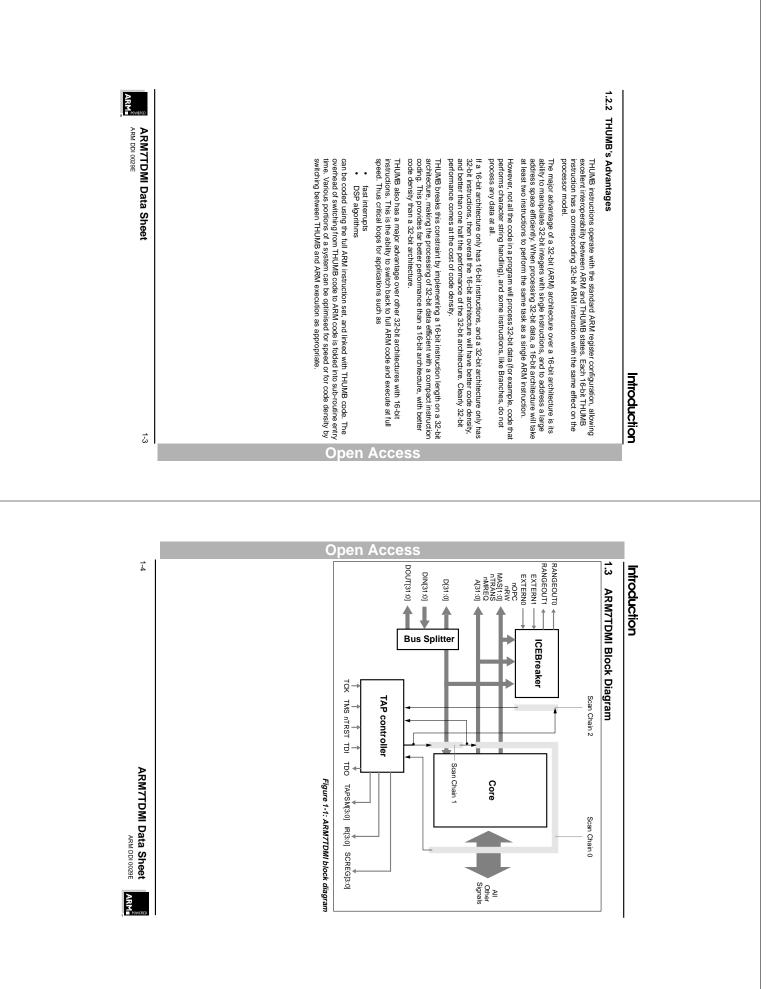

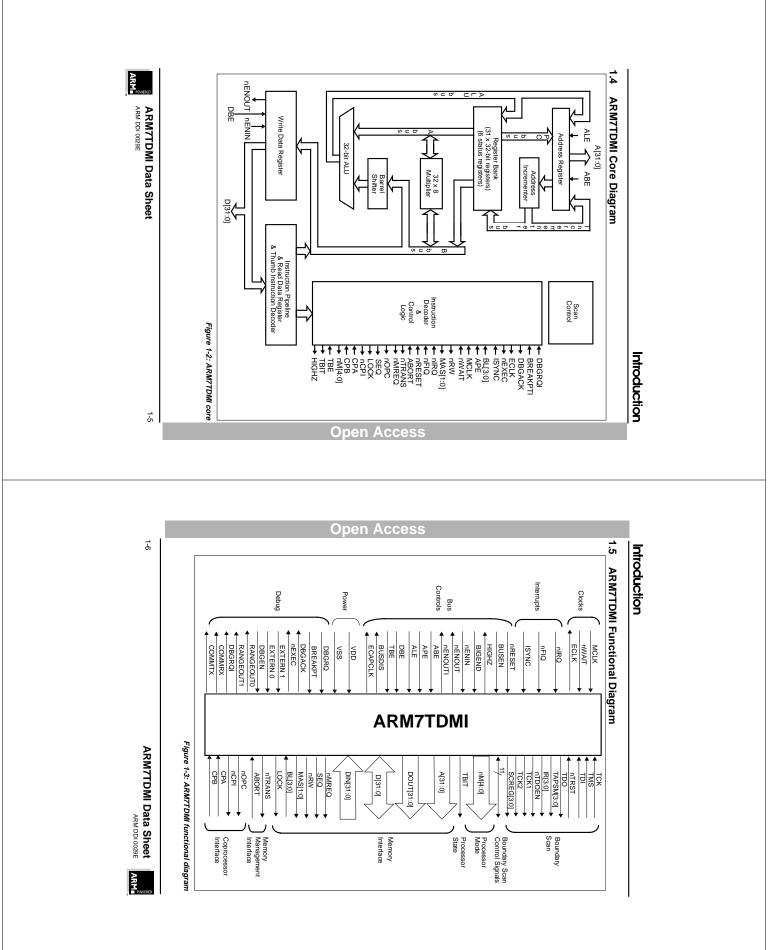

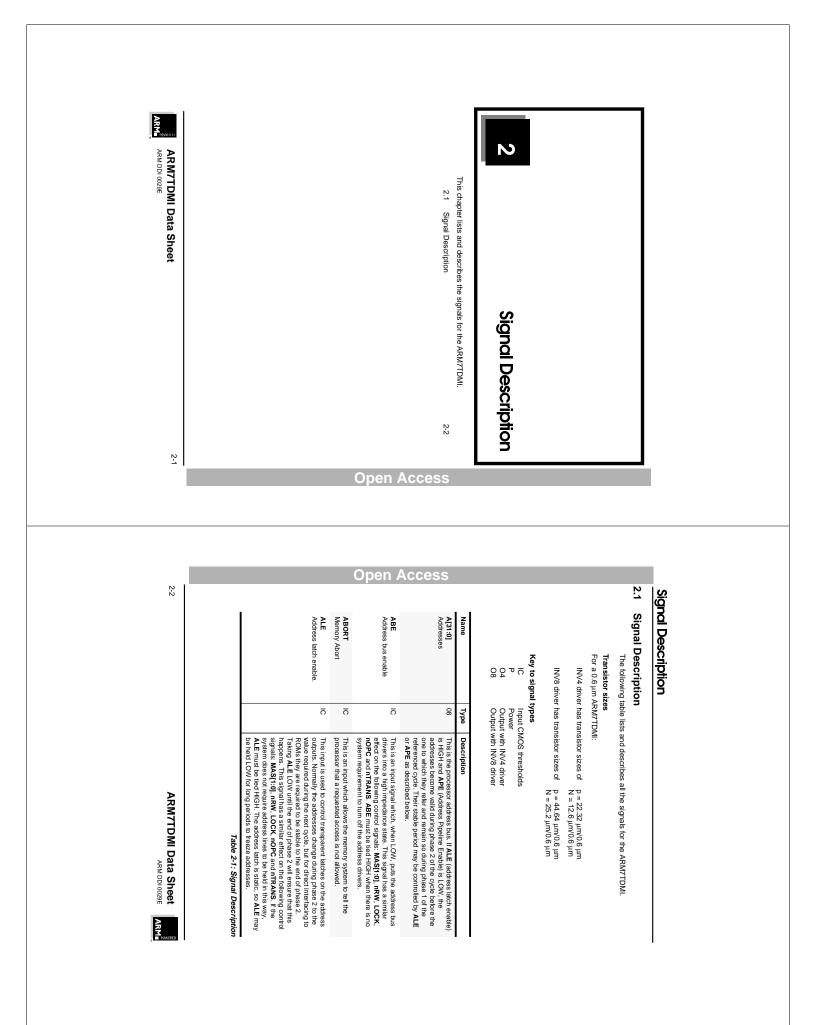

| ARM7TDMI Data Sheet | Introduction<br>1.1 Introduction<br>1.2 Introduction<br>1.2 ARM7TDMI Architecture<br>1.3 ARM7TDMI Block Diagram<br>1.4 ARM7TDMI Block Diagram<br>1.4 ARM7TDMI Core Diagram<br>1.5 ARM7TDMI Functional Diagram<br>2.1 Signal Description<br>2.1 Signal Description<br>2.1 Signal Description<br>2.1 Signal Description<br>2.1 Signal Description<br>3.2 Switching States<br>3.3 Memory Formats<br>3.4 Instruction Length<br>3.5 Data Types<br>3.6 Operating Modes<br>3.7 Registers<br>3.8 The Program Status Registers<br>3.9 Exceptions<br>3.10 Interrupt Latencies<br>3.11 Reset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Contents-i          | <b>Contents</b><br><sup>3</sup> / <sub>5</sub> <sup>3</sup> / <sub>4</sub> <sup>3</sup> / <sub>2</sub> <sup>3</sup> / <sub>2</sub> <sup>3</sup> / <sub>2</sub> <sup>3</sup> / <sub>2</sub> <sup>2</sup> / <sub>2</sub> <sup>1</sup> / <sub>5</sub> <sup>1</sup> / <sub>5</sub> <sup>1</sup> / <sub>4</sub> <sup>1</sup> / <sub>2</sub> <sup>1</sup> |

|                     | Open Access                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Contents-ii         | 4 r0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                     | ARM Instruction Set           4.1         Instruction Set Summ           4.2         The Condition Field           4.3         Branch and Exchang           4.4         Branch and Exchang           4.5         Data Processing           4.6         PRR Transfer (Multiply and Multiply and Multiply Long and Multiply and Fransfer           4.7         Multiple Data Swap (S           4.11         Block Data Transfer           4.12         Single Data Transfer           4.13         Software Interrupt (S           4.14         Coprocessor Data T           4.15         Coprocessor Registe           4.16         Coprocessor Registe           4.17         Undefined Instruction Set           5.1         Format 2: add/subtre           5.2         Format 2: add/subtre           5.3         Format 3: Invove/com           5.4         Format 4: ALU opera           5.51         Format 3: Invove/com           5.51         Format 3: Invove/store           5.51         Format 1: Sold/store           5.51         Format 1: Sold/store           5.51         Format 1: Sinutifiely           5.51         Format 1: Solo                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                               |                               |                                |                               |                                        |                         |                                   |                                |                                            |                                                  |                                           |                            |                                                  |                          |                                               |                        |                                 | ъ                     |                          |                       |                                           |                                       |                                   |                          |                        |                                |                                   |                                 |                                                         |                                             |                         |                 |                                     |                          |                     |                         |

|-------------------------------|-------------------------------|--------------------------------|-------------------------------|----------------------------------------|-------------------------|-----------------------------------|--------------------------------|--------------------------------------------|--------------------------------------------------|-------------------------------------------|----------------------------|--------------------------------------------------|--------------------------|-----------------------------------------------|------------------------|---------------------------------|-----------------------|--------------------------|-----------------------|-------------------------------------------|---------------------------------------|-----------------------------------|--------------------------|------------------------|--------------------------------|-----------------------------------|---------------------------------|---------------------------------------------------------|---------------------------------------------|-------------------------|-----------------|-------------------------------------|--------------------------|---------------------|-------------------------|

| 5.17                          | 5.16                          | 5.15                           | 5.14                          | 5.13                                   | 5.12                    | 5.11                              | 5.10                           | 5.9                                        | 5.8                                              | 5.7                                       | 5.6                        | 5.5                                              | 5.4                      | 5.3                                           | 5.2                    | 5.1                             | THU                   | 4.18                     | 4.17                  | 4.16                                      | 4.15                                  | 4.14                              | 4.13                     | 4.12                   | 4.11                           | 4.10                              | 4.9                             | 4.8                                                     | 4.7                                         | 4.6                     | 4.5             | 4.4                                 | 4.3                      | 4.2                 | 4.1                     |

| Format 17: software interrupt | Format 16: conditional branch | Format 15: multiple load/store | Format 14: push/pop registers | Format 13: add offset to Stack Pointer | Format 12: load address | Format 11: SP-relative load/store | Format 10: load/store halfword | Format 9: load/store with immediate offset | Format 8: load/store sign-extended byte/halfword | Format 7: load/store with register offset | Format 6: PC-relative load | Format 5: Hi register operations/branch exchange | Format 4: ALU operations | Format 3: move/compare/add/subtract immediate | Format 2: add/subtract | Format 1: move shifted register | THUMB Instruction Set | Instruction Set Examples | Undefined Instruction | Coprocessor Register Transfers (MRC, MCR) | Coprocessor Data Transfers (LDC, STC) | Coprocessor Data Operations (CDP) | Software Interrupt (SWI) | Single Data Swap (SWP) | Block Data Transfer (LDM, STM) | Halfword and Signed Data Transfer | Single Data Transfer (LDR, STR) | Multiply Long and Multiply-Accumulate Long (MULL, MLAL) | Multiply and Multiply-Accumulate (MUL, MLA) | PSR Transfer (MRS, MSR) | Data Processing | Branch and Branch with Link (B, BL) | Branch and Exchange (BX) | The Condition Field | Instruction Set Summary |

| 5-38                          | 5-36                          | 5-34                           | 5-32                          | 5-30                                   | 5-28                    | 5-26                              | 5-24                           | 5-22                                       | 5-20                                             | 5-18                                      | 5-16                       | 5-13                                             | 5-11                     | 5-9                                           | 5-7                    | ი<br>ი                          | 5                     | 4-61                     | 4-60                  | 4-57                                      | 4-53                                  | 4-51                              | 4-49                     | 4-47                   | 4-40                           | 4-34                              | 4-28                            | 4-25                                                    | 4-23                                        | 4-18                    | 4-10            | 4-8                                 | 4-6                      | 4-5                 | 4-2                     |

<u>4</u>

ARM7TDMI Data Sheet ARM

| ARM7TDMI Data Sheet |              |                       |                         |       |                                 |                                       |                      |                     |                     |                      |                  |       |                                |                         |               |          | 8               |                        |             |                         |                         |                   |          | 7                     |                       |                  |                         |                   |                   |                   |                    |                |             |          | 6                |                          |                                  |                                 |          |

|---------------------|--------------|-----------------------|-------------------------|-------|---------------------------------|---------------------------------------|----------------------|---------------------|---------------------|----------------------|------------------|-------|--------------------------------|-------------------------|---------------|----------|-----------------|------------------------|-------------|-------------------------|-------------------------|-------------------|----------|-----------------------|-----------------------|------------------|-------------------------|-------------------|-------------------|-------------------|--------------------|----------------|-------------|----------|------------------|--------------------------|----------------------------------|---------------------------------|----------|

| Data                | 8.15         | 8.14                  | 8.13                    | 0.14  | 8 13                            | 8.11                                  | 8.10                 | 8.9                 | 8.8                 | 8.7                  | 8.6              | 8.5   | 8.4                            | 8.3                     | 8.2           | 8.1      | Debu            | 7.6                    | 7.5         | 7.4                     | 7.3                     | 7.2               | 7.1      | Cop                   | 6.10                  | 6.9              | 6.8                     | 6.7               | 6.6               | 6.5               | 6.4                | 6.3            | 6.2         | 6.1      | Mem              | 5.20                     | 5.19                             | 5.18                            |          |

| a Sheet             | Debug Timing | Scan Interface Timing | Priorities / Exceptions |       | The PC's Behaviour During Debug | Determining the Core and System State | ARM7TDMI Core Clocks | Test Data Registers | Public Instructions | Instruction Register | Pullup Resistors | Reset | Scan Chains and JTAG Interface | Debug Interface Signals | Debug Systems | Overview | Debug Interface | Undefined Instructions | Idempotency | Privileged Instructions | Register Transfer Cycle | Interface Signals | Overview | Coprocessor Interface | The External Data Bus | The ARM Data Bus | Stretching Access Times | Locked Operations | Memory Management | Instruction Fetch | Data Transfer Size | Address Timing | Cycle Types | Overview | Memory Interface | Instruction Set Examples | Format 19: long branch with link | Format 18: unconditional branch |          |

| Contents-iii        | 8-30         | 8-26                  | 8-25                    | 0.420 | 2.23                            | 8-19                                  | 8-18                 | 8-12                | 6-8                 | - 8-9                | 6-8              | 8-8   | 8-6                            | 8-3                     | 8-2           | 8-2      | <u>چ</u>        | 7-4<br>N               | 7-4<br>A    |                         |                         |                   |          | 7-1                   | 6-15                  | 6-13             | 6-12                    | 6-12              | 6-12              | 6-10              | 6-9                | 6-4            | 6-2         | 6-2      | 6-1              | 5-42                     | 5-40                             | 5-39                            | Contents |

|                     |              |                       |                         |       |                                 |                                       |                      |                     |                     |                      |                  |       |                                |                         |               | 0        | ре              | 'n                     | A           | co                      | ce                      | s                 | S        |                       |                       |                  |                         |                   |                   |                   |                    |                |             |          |                  |                          |                                  |                                 |          |

| Contents-iv         |              |                       |                         |       |                                 |                                       |                      |                     |                     |                      |                  |       |                                |                         |               |          |                 |                        |             |                         |                         |                   |          |                       |                       |                  |                         |                   |                   |                   |                    |                |             |          |                  |                          |                                  |                                 |          |

| 4                                                                              | و<br>0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|--------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>DC P:</b><br>11.1<br>11.2                                                   | ICEB<br>9.1<br>9.2<br>9.3<br>9.4<br>9.5<br>9.4<br>9.4<br>9.5<br>9.4<br>9.5<br>9.5<br>9.6<br>9.7<br>9.8<br>9.9<br>9.1<br>10.1<br>10.2<br>10.5<br>10.5<br>10.5<br>10.5<br>10.1<br>10.1<br>10.1<br>10.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

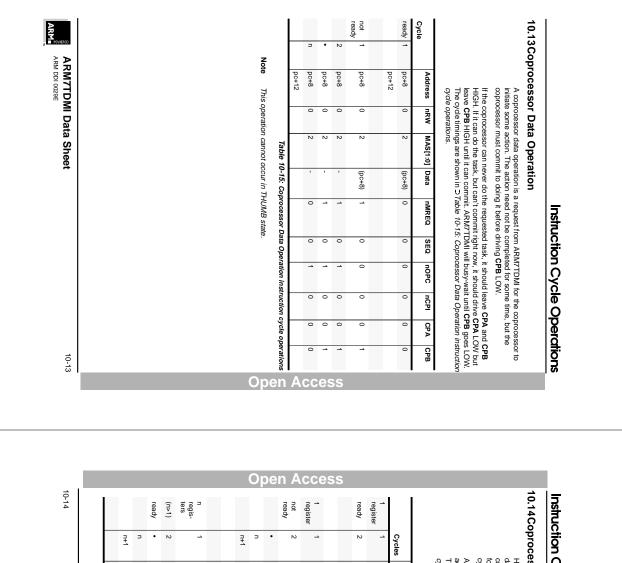

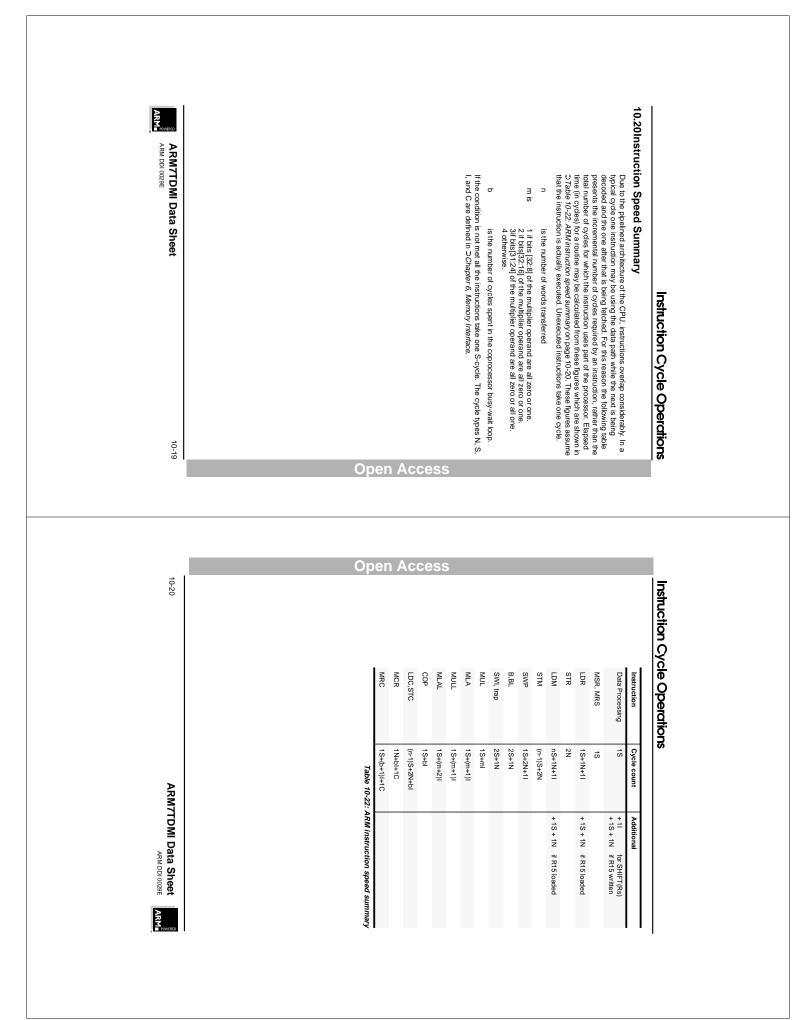

| DC Parameters<br>11.1 Absolute Maximum Ratings<br>11.2 DC Operating Conditions | ICEBreaker Module         9.1       Overview         9.2       The Watchpoint Register         9.3       Programming Breakpoints         9.4       Programming Breakpoints         9.5       The Debug Control Register         9.6       Debug Status Register         9.7       Coupling Breakpoints and Watchpoints         9.8       Disabling ICEBreaker Timing         9.1       Debug Communications Channel         9.1       Debug Communications Channel         9.1       Debug Communications Channel         9.11       Debug Communications Channel         9.11       Debug Communications Channel         9.11       Debug Communications Channel         10.1       Introduction         10.1       Introduction         10.2       Branch and Branch with Link         10.3       THUMB Branch with Link         10.4       Branch and Exchange (BX)         10.5       Data Operations         10.6       Multiple Register         10.7       Load Register         10.8       Store Multiple Registers         10.10       Store Multiple Register Transfer (trom coprocessor to memory)         10.13       Coprocessor Data Transfer (trom coproc |

| <b>11-1</b><br>11-2<br>11-2                                                    | 92<br>92<br>92<br>92<br>94<br>94<br>94<br>94<br>94<br>94<br>94<br>94<br>94<br>94<br>94<br>94<br>94                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

ARM7TDMI Data Sheet

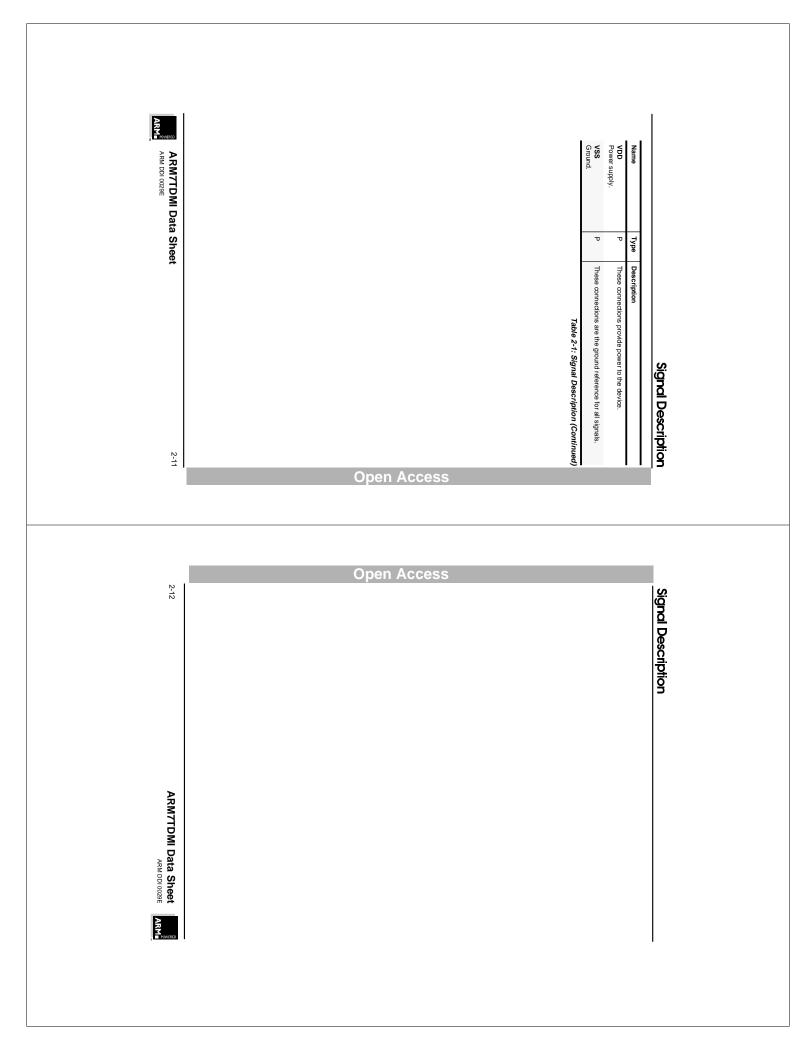

| Type | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ō    | When HIGH, this signal enables the address timing pipeline. In this state, the address bus plus MA3[1:0], nFW, nTRANS, LOCK and nOPC change in the phase 2 prior to the memory cycle to which they refer. When APE is LOW, these signals change in the phase 1 of the actual cycle. Please refer to 2 <i>Chapter 6, Memory Interface</i> for details of this timing.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| ō    | When this signal is HIGH the processor treats bytes in memory<br>as being in Big Endian format. When it is LOW, memory is<br>treated as Little Endian.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| ō    | These signals control when data and instructions are latched from the external data bus. When BL[3] is HIGH, the data on D[31:24] is latched on the failing edge of MCLK. When BL[2] is HIGH, the data on D[23:16] is latched and so on. Please refer to C Chapter 6. <i>Memory Interface</i> for details on the use of these signals.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| ō    | This signal allows external hardware to halt the execution of the<br>processor for debug purposes. When HGH causes the current<br>memory access to be breakpointed. If the memory access is an<br>instruction facth, ARN/TDM will enter debug state if the<br>instruction reaches the execute stage of the ARM/TDM pipeline.<br>If the memory access is for data, ARM/TDM will enter debug<br>state after the current instruction completes execution. This<br>allows extension of the internal breakpoints provided by the<br>ICEBreaker module. See D Chapter 9, <i>ICEBreaker Module</i> .                                                                                                                                                                                                                                                                                |

| 0    | This signal is HIGH when INTEST is selected on scan chain 0 or<br>4 and may be used to disable external logic driving onto the<br>bidrectional data bus during scan testing. This signal changes on<br>the falling edge of <b>TCK</b> .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| ō    | This is a static configuration signal which determines whether the<br>bidirectional data bus. <b>D[31:0]</b> , or the undiffered on all data busses,<br><b>DIN(31:0]</b> and <b>DOUT[31:0]</b> , are be used for transfer of data<br>between the processor and memory. Refer also to $2$ <i>Chapter 6</i> ,<br><i>Memory Interface</i> . <b>UOV</b> , the bidirectional data bus, <b>D[31:0]</b> is<br>when <b>BUSEN</b> is LOW, the bidirectional data bus, <b>D[31:0]</b> is<br>used. In this case, <b>DOUT[31:0]</b> is driven to value doc0000000,<br>and any data presented on <b>DIN[31:0]</b> is grared.<br>When <b>BUSEN</b> is HIGH, the bidirectional data bus, <b>D[31:0]</b> is<br>ignored and must be left unconnected. Input data and<br>instructions are presented on <b>binut</b> data bus, <b>DIN[31:0]</b> ,<br>output data appears on <b>DOUT[31:0]</b> . |

| 0    | When HIGH, this signal denotes that the comms channel receive<br>buffer is empty. This signal changes on the rising edge of MCLK.<br>See 3.9.11 Debug Communications Channel on page 9-14<br>for more information on the debug comms channel.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|      | Table 2-1: Signal Description (Continued)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

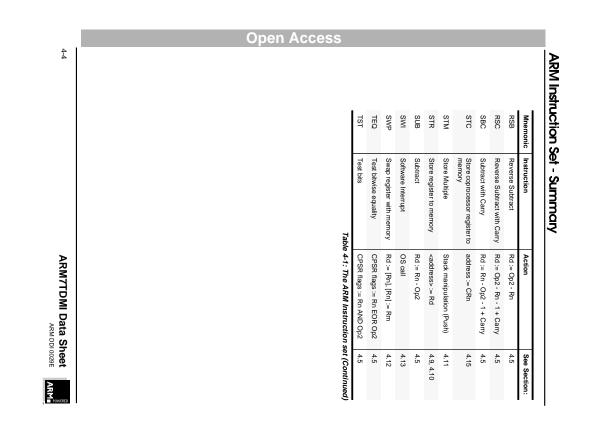

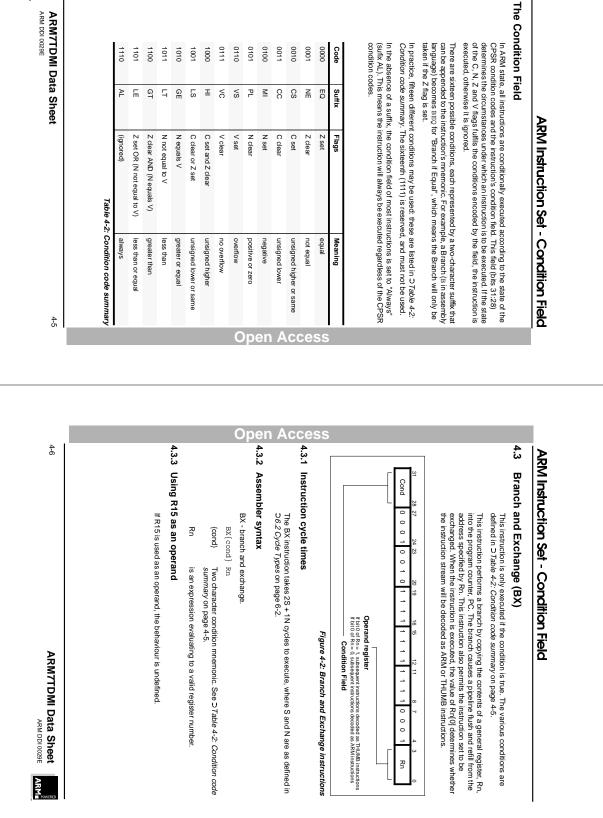

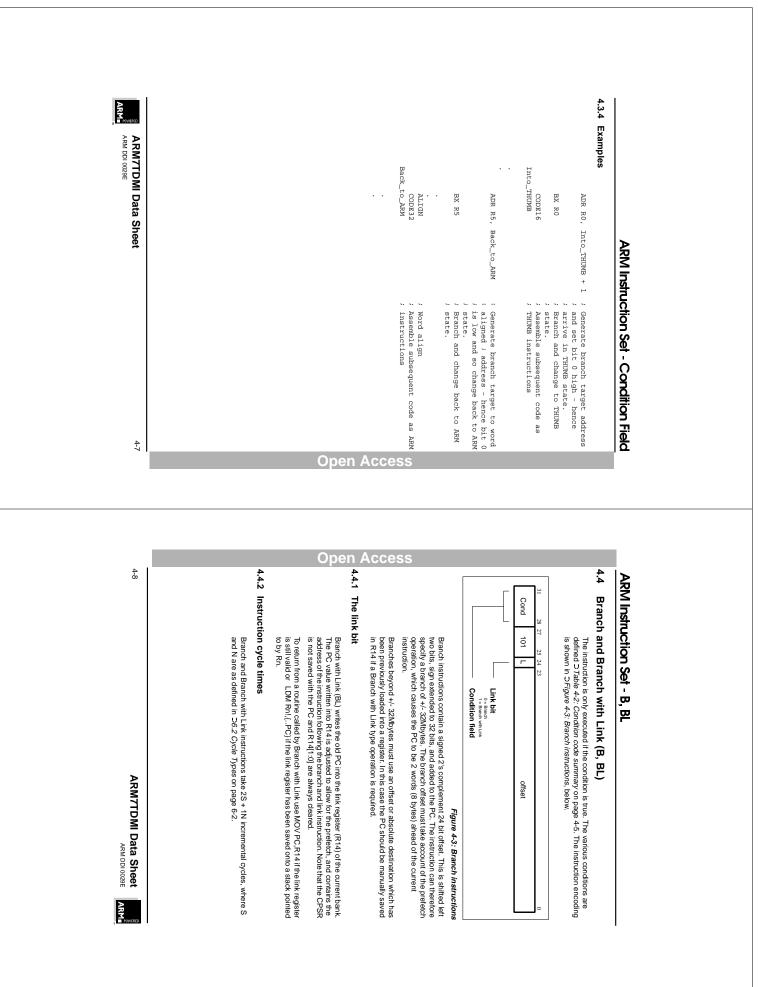

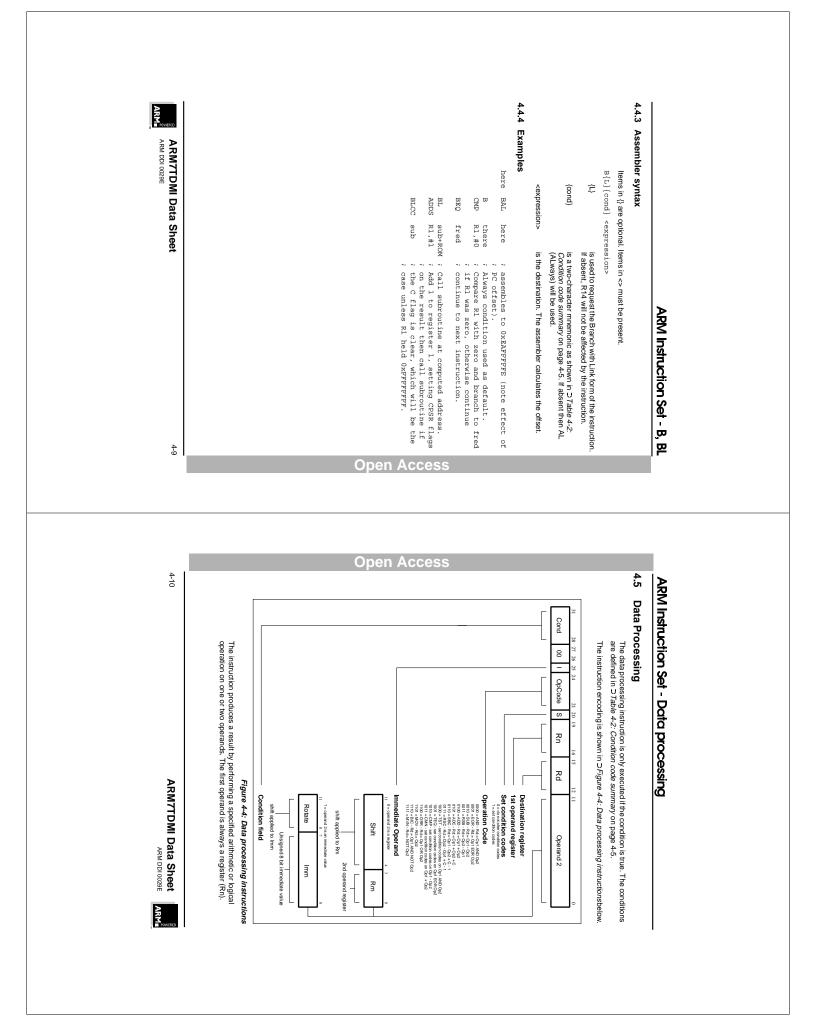

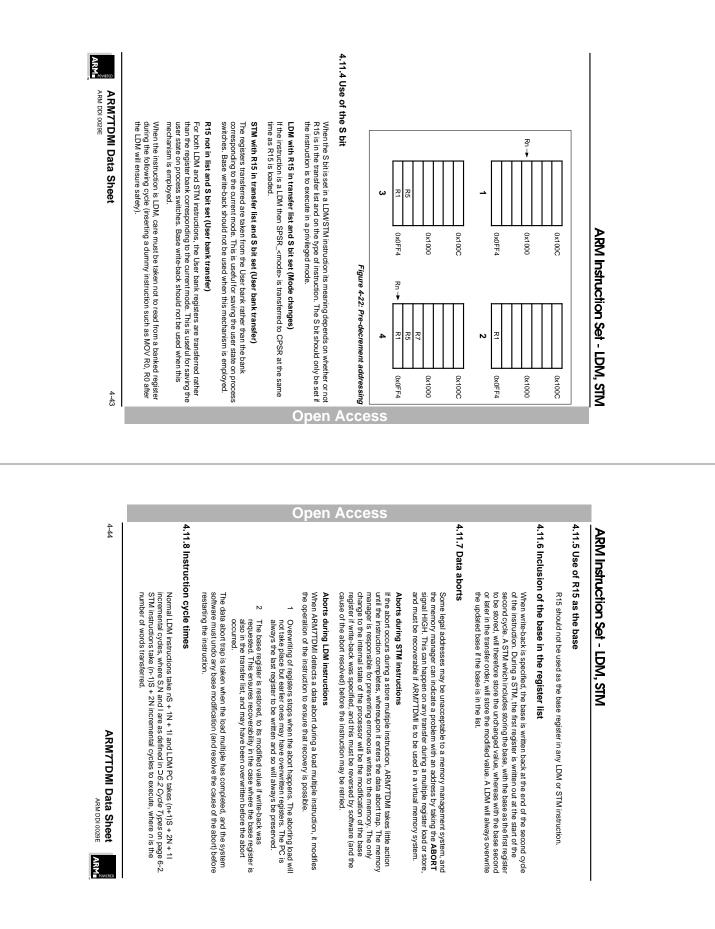

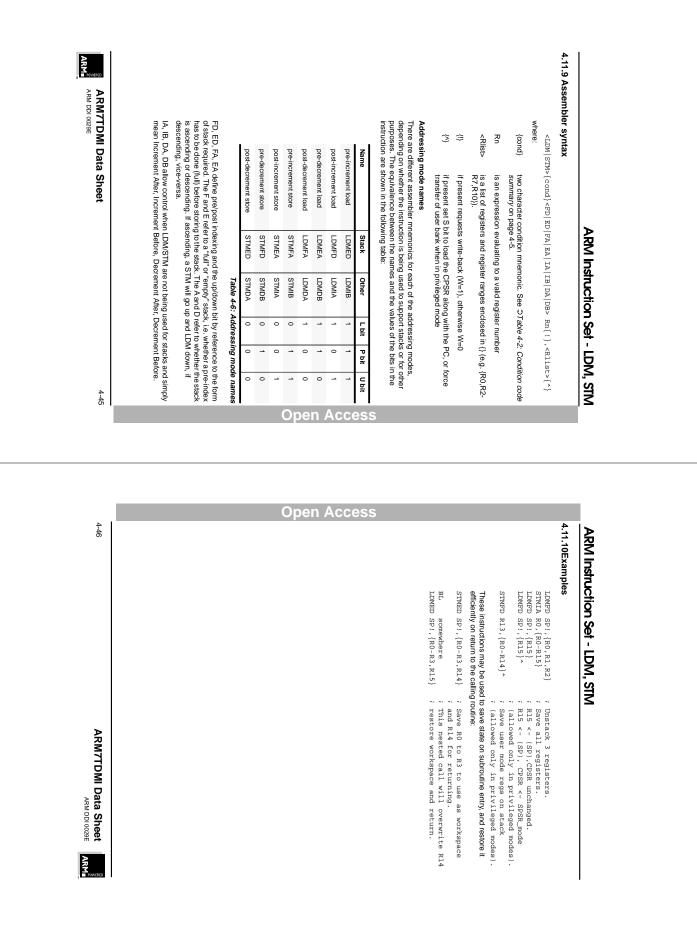

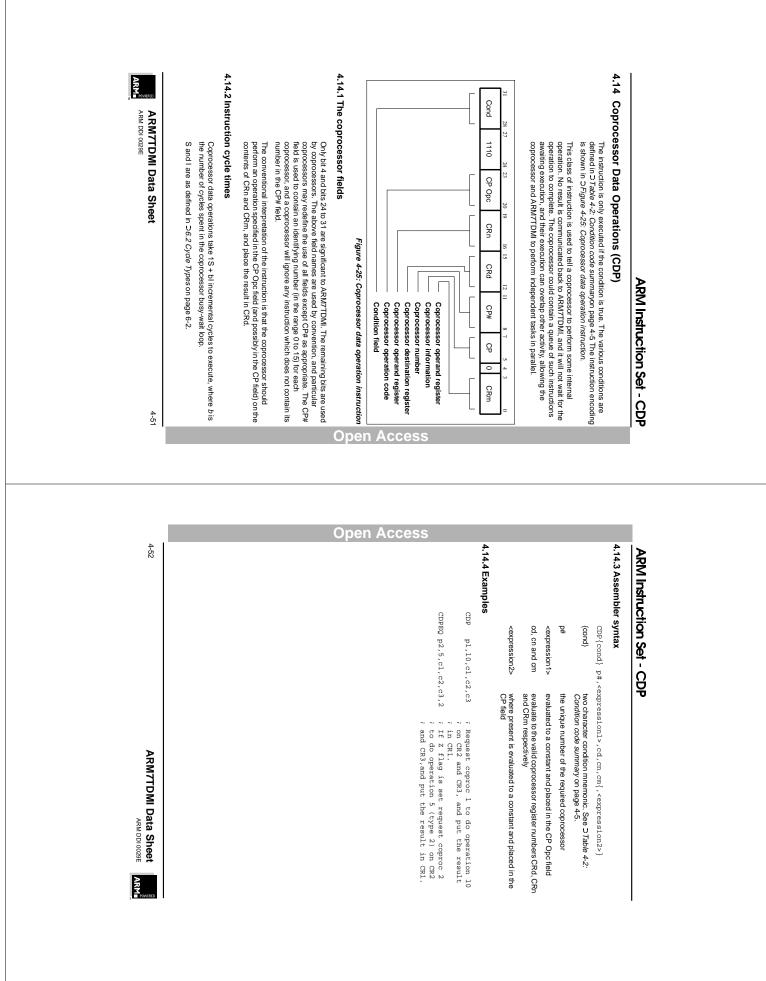

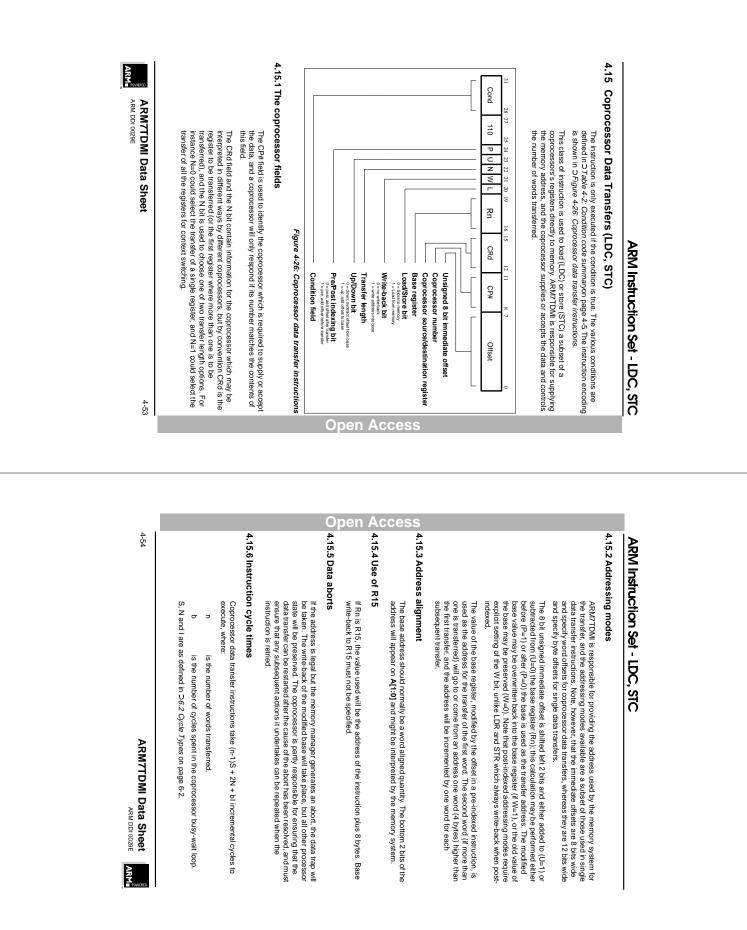

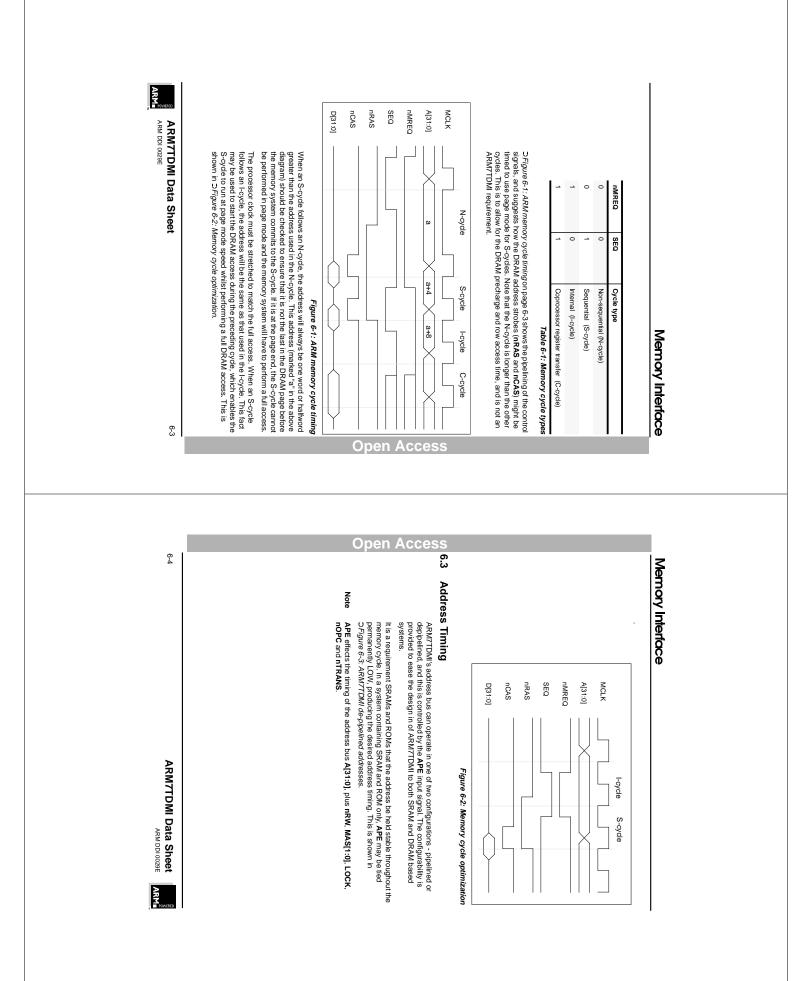

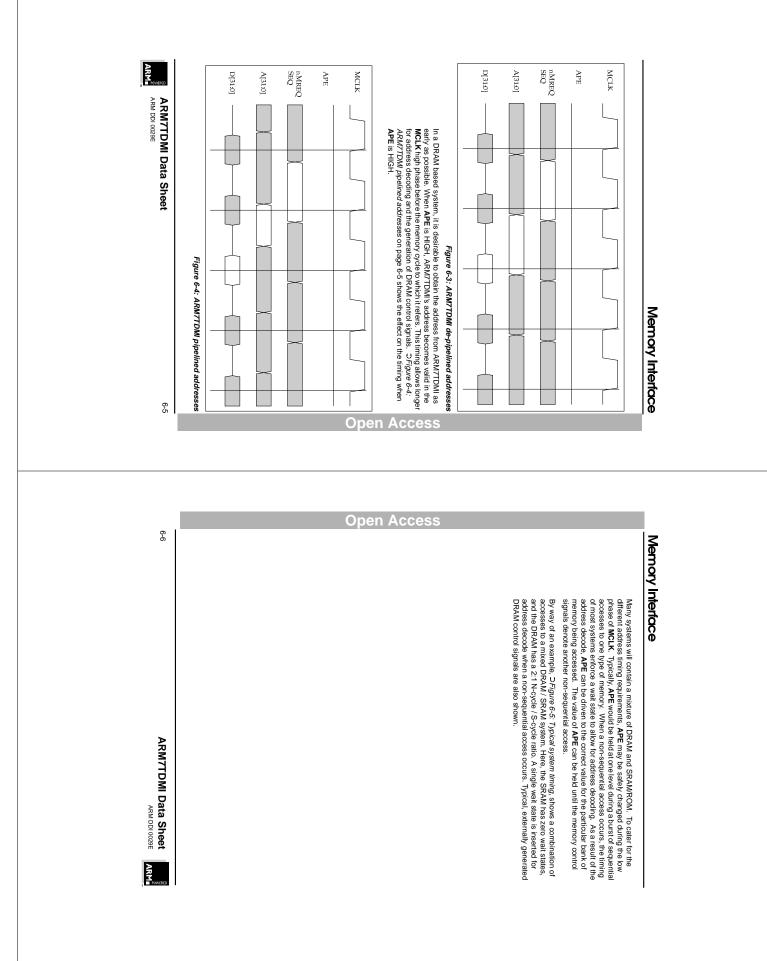

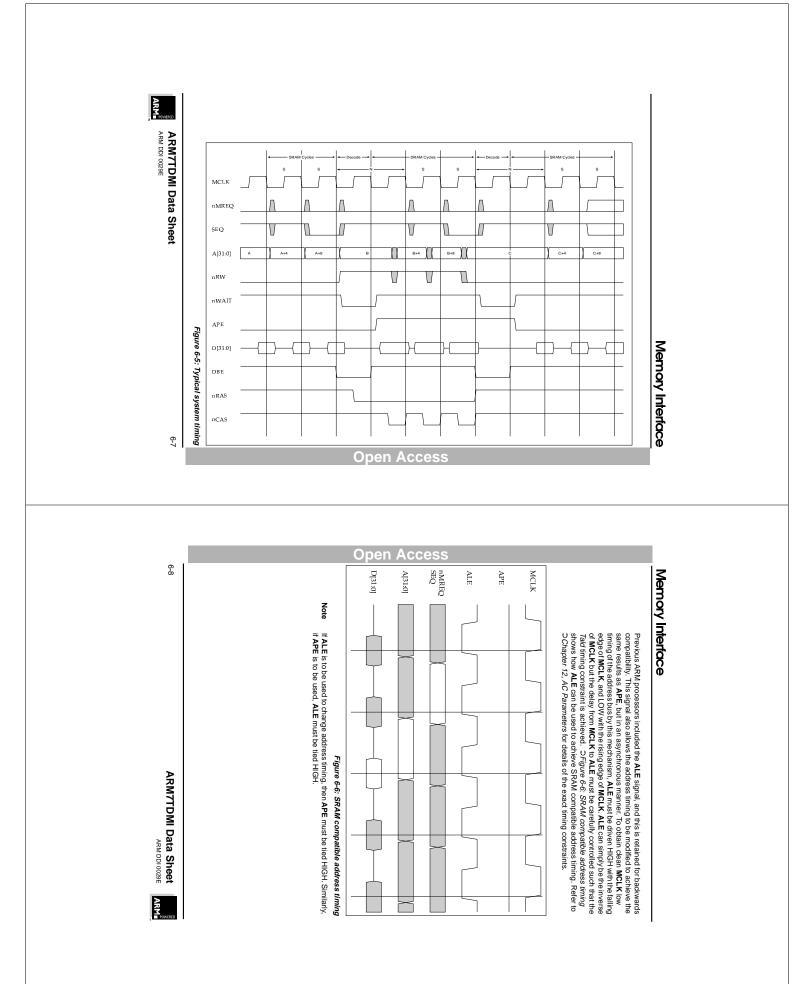

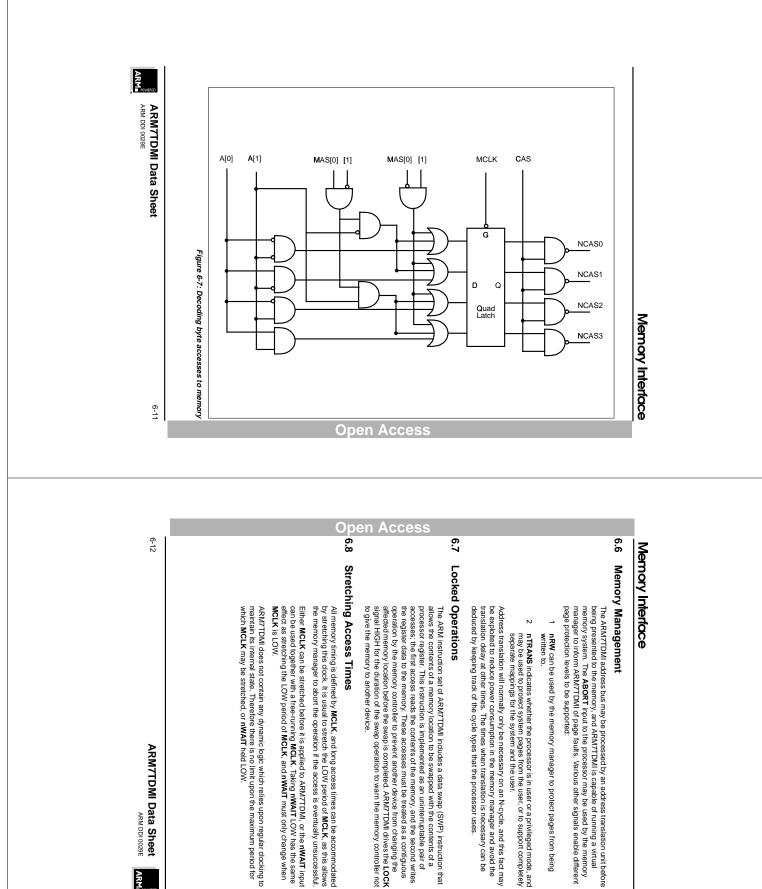

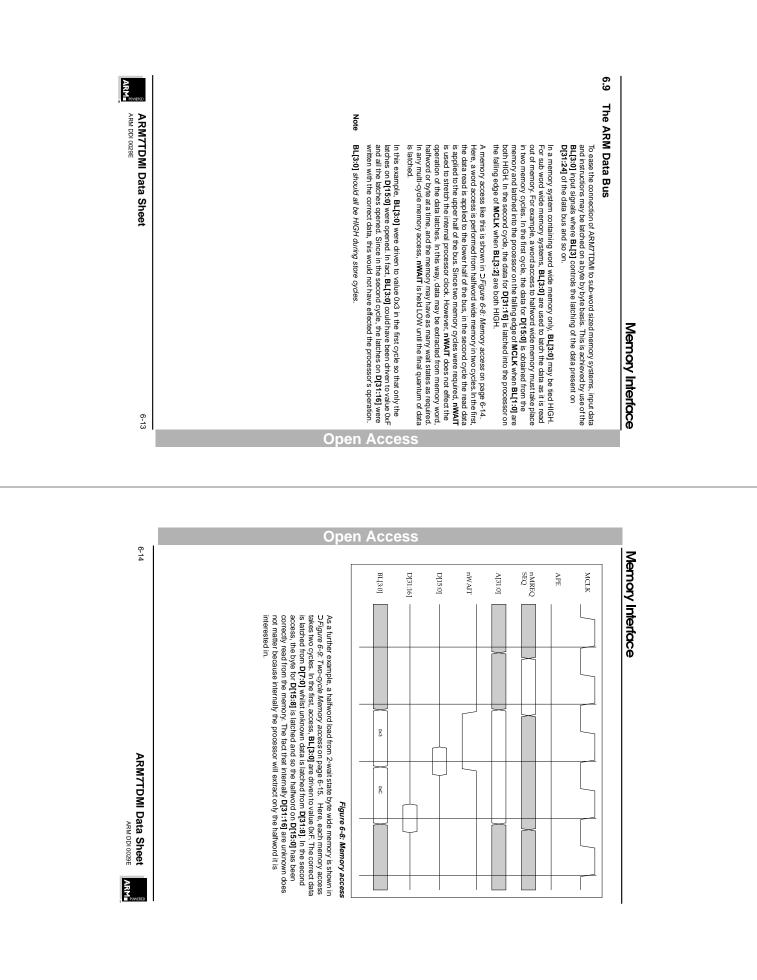

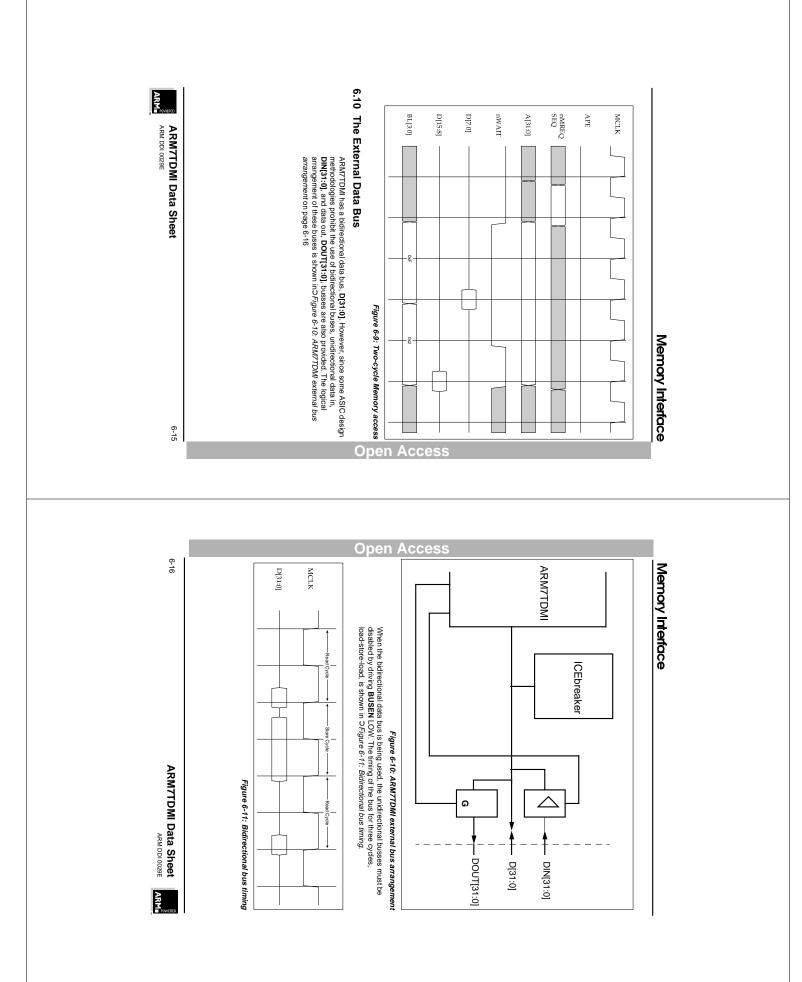

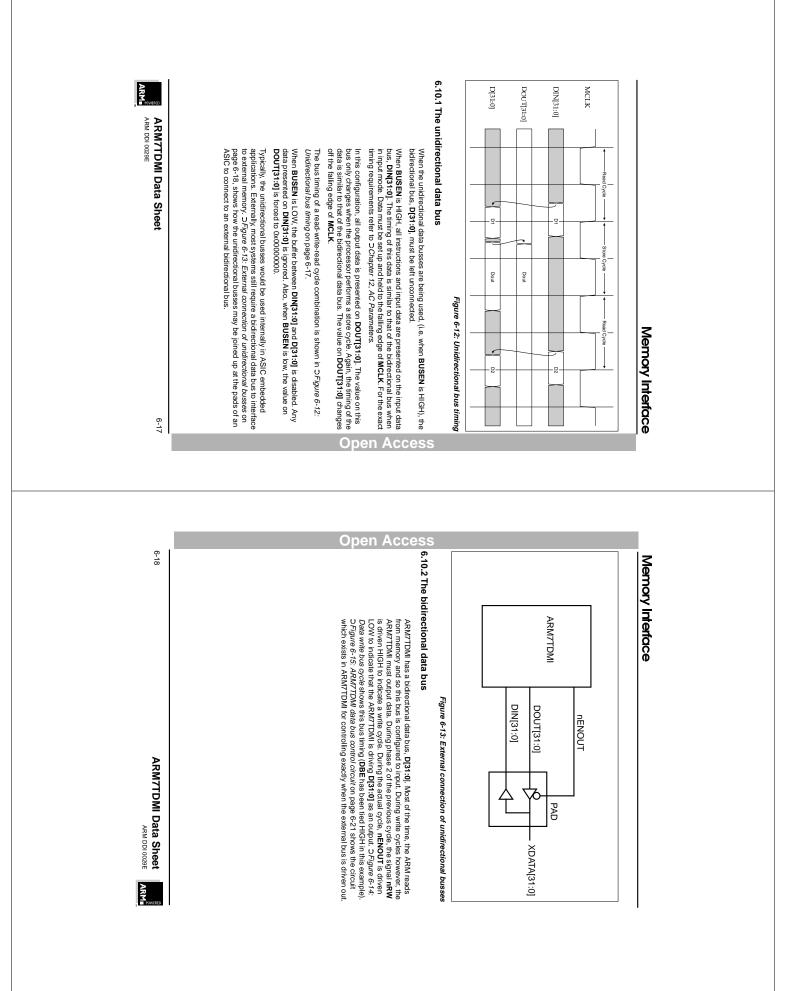

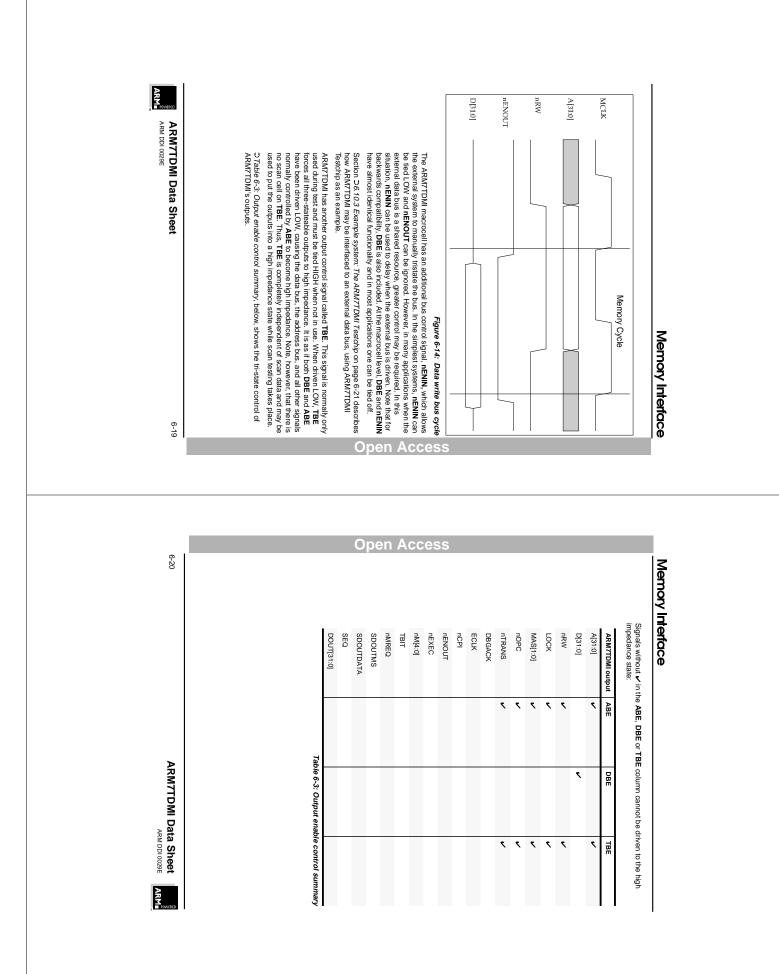

|      | ame     Type       gress pipeline enable.     IC       GEND     IC       gendian configuration.     IC       gendian configuration.     IC       gendian configuration.     IC       us Disable     IC       serve     IC       us Disable     IC       serve     IC       us Disable     IC       serve     IC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |