## **ARM Developer Suite**

Version 1.0.1

**Debug Target Guide**

Copyright © 1999, 2000 ARM Limited. All rights reserved. ARM DUI0058B Copyright © 1999 and 2000 ARM Limited. All rights reserved.

#### **Release Information**

The following changes have been made to this book.

|              |       |               | ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, |

|--------------|-------|---------------|-----------------------------------------|

| Date         | Issue | Change        |                                         |

| October 1999 | А     | Release 1.0   |                                         |

| March 2000   | В     | Release 1.0.1 |                                         |

#### **Proprietary Notice**

ARM, the ARM Powered logo, Thumb, and StrongARM are registered trademarks of ARM Limited.

The ARM logo, AMBA, Angel, ARMulator, EmbeddedICE, ModelGen, Multi-ICE, PrimeCell, ARM7TDMI, ARM7TDMI, ARM9TDMI, ARM9E-S, ETM7, ETM9, TDMI, STRONG, are trademarks of ARM Limited.

All other products or services mentioned herein may be trademarks of their respective owners.

Neither the whole nor any part of the information contained in, or the product described in, this document may be adapted or reproduced in any material form except with the prior written permission of the copyright holder.

The product described in this document is subject to continuous developments and improvements. All particulars of the product and its use contained in this document are given by ARM in good faith. However, all warranties implied or expressed, including but not limited to implied warranties of merchantability, or fitness for purpose, are excluded.

This document is intended only to assist the reader in the use of the product. ARM Limited shall not be liable for any loss or damage arising from the use of any information in this document, or any error or omission in such information, or any incorrect use of the product.

Change History

# Contents **Debug Target Guide**

|           | Prefa | ace                          |      |

|-----------|-------|------------------------------|------|

|           |       | About this book              | viii |

|           |       | Feedback                     | xii  |

| Chapter 1 | Intro | duction                      |      |

|           | 1.1   | About debug support          | 1-2  |

|           | 1.2   | ARMulator                    | 1-3  |

|           | 1.3   | Angel                        | 1-3  |

|           | 1.4   | Semihosting SWIs             | 1-3  |

| Chapter 2 | ARM   | Iulator Basics               |      |

|           | 2.1   | About ARMulator              |      |

|           | 2.2   | ARMulator components         | 2-3  |

|           | 2.3   | Tracer                       | 2-5  |

|           | 2.4   | Profiler                     | 2-11 |

|           | 2.5   | Pagetable module             |      |

|           | 2.6   | Flat memory model            | 2-18 |

|           | 2.7   | Fast memory model            |      |

|           | 2.8   | Memory model with memory map | 2-20 |

|           | 2.9   | DummyMMU                     |      |

|           | 2.10  | Angel                        | 2-24 |

|           | 2.11  | Peripheral models            |      |

|           |       |                              |      |

|           | 2.12  | Other models                                   | 2-29  |

|-----------|-------|------------------------------------------------|-------|

|           | 2.13  | Basic ARM ten system                           | 2-31  |

| Chapter 3 | Writi | ng ARMulator Models                            |       |

|           | 3.1   | Adding models to ARMulator                     | 3-2   |

|           | 3.2   | Writing a new peripheral model                 |       |

|           | 3.3   | Writing a new cache model                      |       |

|           | 3.4   | Rebuilding ARMulator                           |       |

|           | 3.5   | Configuring ARMulator to use the example       |       |

| Chapter 4 | ARM   | ulator Reference                               |       |

| •         | 4.1   | ARMulator models                               | 4-3   |

|           | 4.2   | Basic model interface                          | 4-4   |

|           | 4.3   | The memory interface                           | 4-10  |

|           | 4.4   | Memory model interface                         | 4-14  |

|           | 4.5   | Coprocessor model interface                    | 4-23  |

|           | 4.6   | Operating system or debug monitor interface    |       |

|           | 4.7   | Using the floating-point emulator              |       |

|           | 4.8   | Accessing ARMulator state                      |       |

|           | 4.9   | Exceptions                                     | 4-51  |

|           | 4.10  | Upcalls                                        | 4-53  |

|           | 4.11  | Memory access functions                        | 4-65  |

|           | 4.12  | Event scheduling functions                     | 4-67  |

|           | 4.13  | General purpose functions                      | 4-77  |

|           | 4.14  | Accessing the debugger                         | 4-85  |

|           | 4.15  | Tracer                                         | 4-89  |

|           | 4.16  | Events                                         | 4-91  |

|           | 4.17  | Map files                                      | 4-94  |

|           | 4.18  | armul.cnf, the ARMulator configuration file    | 4-98  |

|           | 4.19  | ToolConf                                       | 4-108 |

|           | 4.20  | Basic ARM ten system configuration trace files | 4-114 |

|           | 4.21  | Reference peripherals                          | 4-121 |

| Chapter 5 | Ange  |                                                |       |

|           | 5.1   | About Angel                                    | 5-2   |

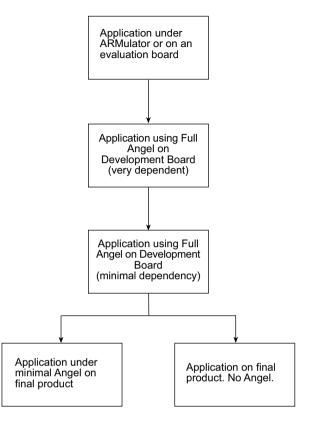

|           | 5.2   | Developing applications with Angel             |       |

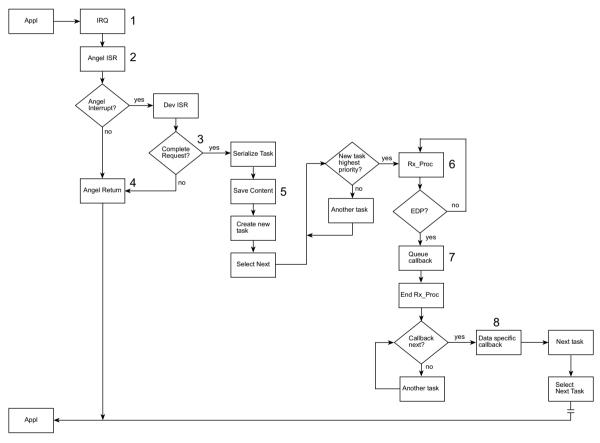

|           | 5.3   | Angel in operation                             |       |

|           | 5.4   | Configuring Angel                              |       |

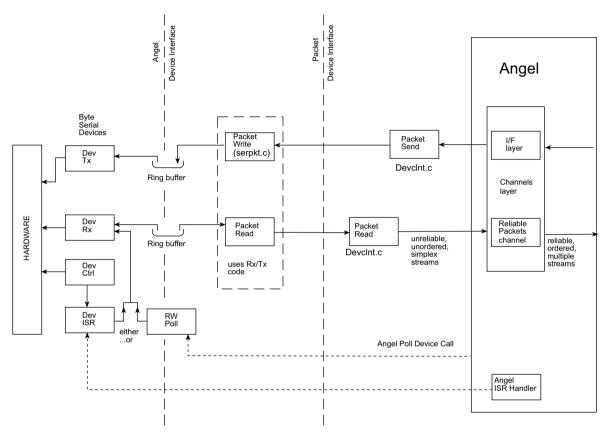

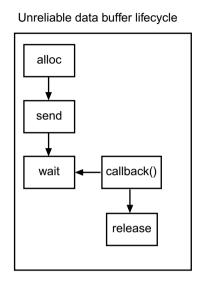

|           | 5.5   | Angel communications architecture              |       |

|           | 5.6   | The Fusion IP stack for Angel                  |       |

| Chapter 6 | Semi  | ihosting SWIs                                  |       |

|           | 6.1   | Overview of the C library support SWIs         | 6-2   |

|           | 6.2   | Semihosting implementation                     |       |

|           | 6.3   | Adding an application SWI handler              |       |

|           | 6.4   | Input/Output SWIs                              |       |

|           | 2     | h                                              |       |

| 6.5 | Debug agent interaction SWIs |  | 6-23 |

|-----|------------------------------|--|------|

|-----|------------------------------|--|------|

### Preface

This preface introduces the ARM debug targets and their reference documentation. It contains the following sections:

- About this book on page Preface-viii

- *Feedback* on page Preface-xii

#### About this book

This book provides reference information for the *ARM Developer Suite* (ADS). It describes:

- ARMulator, the ARM simulator

- Angel, the ARM debug monitor

- Semihosting SWIs, the means for your ARM programs to access facilities on your host computer.

#### Intended audience

This book is written for all developers who are using the ARM debuggers, armsd, AXD, ADU or ADW. It assumes that you are an experienced software developer, and that you are familiar with the ARM development tools as described in *Getting Started*.

#### Using this book

This book is organized into the following chapters:

#### Chapter 1 Introduction

Read this chapter for an introduction to the material in this book.

#### Chapter 2 ARMulator Basics

Read this chapter for a description of ARMulator, the ARM instruction set simulator.

#### Chapter 3 Writing ARMulator Models

Read this chapter for help in writing your own extensions and modifications to ARMulator.

#### Chapter 4 ARMulator Reference

This chapter provides further details to help you use ARMulator.

#### Chapter 5 Angel

Read this chapter for a description of Angel, the ARM debug monitor.

#### Chapter 6 Semihosting SWIs

Read this chapter for information about how to access facilities on the host computer from your ARM programs.

#### **Typographical conventions**

The following typographical conventions are used in this book:

- typewriter Denotes text that may be entered at the keyboard, such as commands, file and program names, and source code.

- typewriter Denotes a permitted abbreviation for a command or option. The underlined text may be entered instead of the full command or option name.

typewriter italic

Denotes arguments to commands and functions where the argument is to be replaced by a specific value.

- *italic* Highlights important notes, introduces special terminology, denotes internal cross-references, and citations.

- **bold** Highlights interface elements, such as menu names and buttons. Also used for terms in descriptive lists, where appropriate.

#### typewriter bold

Denotes language keywords when used outside example code and ARM processor signal names.

#### **Further reading**

This section lists publications from both ARM Limited and third parties that provide additional information on developing code for the ARM family of processors.

ARM periodically provides updates and corrections to its documentation. See http://www.arm.com for current errata sheets and addenda.

See also the ARM Frequently Asked Questions list at: http://www.arm.com/DevSupp/Sales+Support/faq.html

#### **ARM** publications

This book contains information that is specific to the versions of ARMulator, Angel and the semihosting SWIs supplied with the *ARM Developer Suite* (ADS). Refer to the following books in the ADS document suite for information on other components of ADS:

- *Getting Started* (ARM DUI 0064A)

- ADS Tools Guide (ARM DUI 0067A)

- ADS Debuggers Guide (ARM DUI 0066A)

- ADS Developer Guide (ARM DUI 0056A).

The following additional documentation is provided with the ARM Developer Suite:

- ARM Architecture Reference Manual (ARM DUI 0100). This is supplied in Dynatext format, and in PDF format in Install\_directory\PDF\ARM-DDI0100B\_armarm.pdf.

- *ARM Applications Library Programmer's Guide* (ARM DUI 0081). This is supplied in Dynatext format, and in PDF format on the CD.

- *ARM ELF specification* (SWS ESPC 0003). This is supplied in PDF format in *Install\_directory*\PDF\specs\ARM ELFA08.pdf.

- *TIS DWARF 2 specification*. This is supplied in PDF format in *Install\_directory*\PDF\specs\TIS-DWARF2.pdf.

- Angel Debug Protocol. This is supplied in PDF format in Install\_directory\PDF\specs\ADP ARM-DUI0052C.pdf

- Angel Debug Protocol Messages. This is supplied in PDF format in Install\_directory\PDF\specs\ADP ARM-DUI0053D.pdf

In addition, refer to the following documentation for specific information relating to ARM products:

- ARM Reference Peripheral Specification (ARM DDI 0062)

- the ARM datasheet or technical reference manual for your hardware device.

#### Feedback

ARM Limited welcomes feedback on both the ARM Developer Suite, and its documentation.

#### Feedback on the ARM Developer Suite

If you have any problems with the ARM Developer Suite, please contact your supplier. To help us provide a rapid and useful response, please give:

- details of the release you are using

- details of the platform you are running on, such as the hardware platform, operating system type and version

- a small stand-alone sample of code that reproduces the problem

- a clear explanation of what you expected to happen, and what actually happened

- the commands you used, including any command-line options

- sample output illustrating the problem

- the version number of the tool, including the version number and build number.

#### Feedback on this book

If you have any problems with this book, please send email to  ${\tt errata@arm.com}$  giving:

- the document title

- the document number

- the page number(s) to which you comments apply

- a concise explanation of your comments.

General suggestions for additions and improvements are also welcome.

## Chapter 1 Introduction

This chapter introduces the debug support facilities provided in the ADS version 1.00. It contains the following sections:

- About debug support on page 1-2

- ARMulator on page 1-3

- Angel on page 1-3

- Semihosting SWIs on page 1-3.

I

#### 1.1 About debug support

The debug support component of ADS consists of ARMulator and Angel.

You can debug your prototype software using any of the debuggers described in *ADS Debuggers Guide*. The debugger runs on your *host computer*. It is connected to a *target system* that your prototype software runs on.

Your target system may be either:

- a software simulator, simulating ARM hardware

- real ARM-based hardware.

ARMulator is a simulator that runs on the same host computer as the debugger (see *ARMulator* on page 1-3).

ARM-based hardware could be an ARM evaluation or development board, a third-party board, or ARM-based hardware of your own design. In addition to the software that you are developing, it may need to run a *debug monitor* to communicate with the debugger.

Angel is the debug monitor supplied with ADS (see Angel on page 1-3).

ARMulator and the debug monitor use *software interrupts* (SWI) and the host computer to handle process requests from the application for initialization, memory management, and I/O. Using the host computer to assist the local function calls is called *semihosting* (see *Semihosting SWIs* on page 1-3).

In-circuit emulators such as EmbeddedICE and Multi-ICE use an alternative method instead of Angel. See the documentation accompanying the hardware for details.

#### 1.2 ARMulator

ARMulator is an instruction set simulator. It is a collection of modules that simulate the instruction sets and architecture of various ARM processors.

You can use ARMulator for software development and for benchmarking ARM-targeted software. It models the instruction set and counts cycles.

#### 1.3 Angel

Angel is a debug monitor. It is designed to help you to develop and debug applications running on ARM-based hardware. Using Angel you can debug applications running in either ARM state or Thumb state.

You can use Angel to:

- evaluate existing application software on real hardware, as opposed to hardware simulation

- develop new software applications on development hardware

- bring into operation new hardware that includes an ARM processor

- port operating systems to ARM-based hardware.

See the following chapters for more information:

- Chapter 5 Angel

- Chapter 6 Semihosting SWIs.

#### 1.4 Semihosting SWIs

The semihosting SWIs provide the mechanism for using applications in a semihosted environment. SWI handling is available for both ARM and Thumb.

You can use the semihosting SWIs to produce applications which work with Angel, ARMulator, or your own SWI handler.

See Chapter 6 Semihosting SWIs for more information.

Introduction

## Chapter 2 ARMulator Basics

This chapter describes ARMulator, a collection of programs that provide software simulation of ARM processors. It contains the following sections:

- About ARMulator on page 2-2

- ARMulator components on page 2-3

- *Tracer* on page 2-5

- *Profiler* on page 2-11

- *Pagetable module* on page 2-12

- *Flat memory model* on page 2-18

- Fast memory model on page 2-19

- *Memory model with memory map* on page 2-20

- DummyMMU on page 2-23

- Angel on page 2-24

- *Peripheral models* on page 2-26

- Other models on page 2-29

- *Basic ARM ten system* on page 2-31.

#### 2.1 About ARMulator

ARMulator is an instruction set simulator. It is a collection of modules that simulate the instruction sets and architecture of various ARM processors. To run software on ARMulator, you must access it either through the ARM symbolic debugger, armsd, or through the ARM GUI debuggers, AXD, ADU, or ADW. See *ADS Debuggers Guide* for details.

ARMulator is suited to software development and benchmarking ARM-targeted software. It models the instruction set and counts cycles.

ARMulator supports a full ANSI C library to allow complete C programs to run on the simulated system. Refer to the library chapter in *ADS Tools Guide* for more information on C and C++ library support. See also Chapter 6 *Semihosting SWIs* for information on the C library semihosting SWIs supported by ARMulator.

ARMulator does not support ARM10 in the same way that it supports other processors. Refer to *Basic ARM ten system* on page 2-31 for further information.

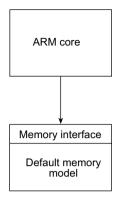

#### 2.2 ARMulator components

This section does not apply to ARM10 systems. For information about ARM10 systems, see *Basic ARM ten system* on page 2-31.

ARMulator consists of a series of modules. The main ones are:

- a model of the ARM processor core

- a model of the memory used by the processor.

There are alternative predefined modules for each of these parts. You can select the combination of processor and memory model you want to use.

One of the predefined memory models, armmap, allows you to specify a simulated memory system in detail.

In addition there are predefined modules which you can use to:

- model additional hardware, such as a coprocessor or peripherals

- model pre-installed software, such as a C library, semihosting SWI handler, or an operating system

- provide debugging or benchmarking information (see *Tracer* on page 2-5 and *Profiler* on page 2-11).

You can use different combinations of predefined modules, and different memory maps, without rebuilding ARMulator (see *Configuring ARMulator* on page 2-4 and *Memory model with memory map* on page 2-20).

You can write your own modules, or edit copies of the predefined ones, if the modules provided do not meet your needs. For example:

- to model a different peripheral, coprocessor, or operating system

- to model a different memory system

- to provide additional debugging or benchmarking information.

The source code of most of the modules, excluding the processor models, is supplied. You can use these as examples to help you write your own modules (see Chapter 3 *Writing ARMulator Models*).

#### 2.2.1 Configuring ARMulator

You can configure some of the details of ARMulator from armsd, AXD, ADU, or ADW. See *ADS Debuggers Guide* for details. The currently active models and configurations are announced in the debugger startup banner

To make other adjustments you must edit ARMulator files directly. These are described in this chapter, in Chapter 3 *Writing ARMulator Models*, and Chapter 4 *ARMulator Reference*.

The following sections describe each of the predefined modules in turn, and how they may be configured.

#### 2.3 Tracer

You can use Tracer to trace instructions, memory accesses, and events. The configuration file armul.cnf controls what is traced (see *armul.cnf, the ARMulator configuration file* on page 4-98).

—— Note ———

Tracer cannot be used with ARM10 systems. See *Basic ARM ten system* on page 2-31 for information about ARM10 systems.

#### 2.3.1 Debugger support for tracing

There is no direct debugger support for tracing. Instead, Tracer uses bit 4 of the RDI logging level (\$rdi\_log) variable to enable or disable tracing.

#### Using AXD

Select System Views $\rightarrow$ Debugger Internals $\rightarrow$ Internal Variables, and then double-click on the  $rdi_log$  value to edit it.

- To enable tracing, set \$rdi\_log to 0x0000010.

- To disable tracing, set \$rdi\_log to 0x0000000.

#### Using ADU or ADW

#### Select Set RDI Log Level from the Options menu.

- To enable tracing, set the RDI log level to 16.

- To disable tracing, set the RDI log level to 0.

#### Using armsd

- To enable tracing under armsd, type \$rdi\_log=16.

- To disable tracing, type \$rdi\_log=0.

#### 2.3.2 Interpreting trace file output

This section describes how you interpret the output from Tracer.

#### Example of a trace file

The following example shows part of a trace file:

```

Date: Fri Jul 16 13:29:16 1999

Source: Armul

Options: Trace Instructions

(Disassemble) Trace Memory Cycles

MNR40____00008008 EB00000C

MSR40___ 0000800C EB00001B

MSR40 00008010 EF000011

IT 00008008 eb00000c BL

0x8040

MNR40 00008040 E1A00000

MSR40___ 00008044 E04EC00F

MSR40____00008048 E08FC00C

IT 00008040 e1a00000 NOP

MSR40 0000804C E99C000F

IT 00008044 e04ec00f SUB

r12,r14,pc

MSR40 00008050 E24CC010

IT 00008048 e08fc00c ADD

r12,pc,r12

E 00000020 0000000 10005

MNR40___ 00000020 E1A00000

IT 00000018 eb00000a BL

0x48

E 00000048 0000000 10005

MNR40____ 00000048 E10F0000

E 0000004C 00000000 10005

MSR40____0000004C E1A00000

```

In a trace file, there are three types of line:

- trace memory entries (M lines)

- trace instruction entries (I lines)

- trace event entries (E lines).

These are described in the following sections.

#### Trace memory (M lines)

Trace memory (M) lines have the following format for general memory accesses:

```

M<type><rw><size>[0][L][S] <address> <data>

```

where:

| <type></type>       | indicates the cycle type:                                                                                                                                                                                                                          |  |

|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                     | s sequential                                                                                                                                                                                                                                       |  |

|                     | N nonsequential.                                                                                                                                                                                                                                   |  |

| <rw></rw>           | indicates either a read or a write operation:                                                                                                                                                                                                      |  |

|                     | R read                                                                                                                                                                                                                                             |  |

|                     | w write.                                                                                                                                                                                                                                           |  |

| <size></size>       | indicates the size of the memory access:                                                                                                                                                                                                           |  |

|                     | 4 word (32 bits)                                                                                                                                                                                                                                   |  |

|                     | 2 halfword (16 bits)                                                                                                                                                                                                                               |  |

|                     | 1 byte (8 bits).                                                                                                                                                                                                                                   |  |

| 0                   | indicates an opcode fetch (instruction fetch).                                                                                                                                                                                                     |  |

| L                   | indicates a locked access.                                                                                                                                                                                                                         |  |

| S                   | indicates a speculative instruction fetch.                                                                                                                                                                                                         |  |

| <address></address> | gives the address in hexadecimal format, for example 00008008.                                                                                                                                                                                     |  |

| <data></data>       | <ul> <li>can show one of the following:</li> <li>value gives the read/written value, for example EB00000C</li> <li>(wait) indicates nWAIT was LOW to insert a wait state</li> <li>(abort) indicates ABORT was HIGH to abort the access.</li> </ul> |  |

Trace memory lines may also have any of the following formats:

- MI for idle cycles

- MC for coprocessor cycles

- MIO for idle cycles on the instruction bus of Harvard architecture processors such as ARM9TDMI.

#### Trace instructions (I lines)

The format of the trace instruction (I) lines is as follows:

[ IT | IS ] <instr\_addr> <opcode> [<disassembly>]

For example:

IT 00008044 e04ec00f SUB r12,r14,pc where: indicates that the instruction was taken. IТ indicates that the instruction was skipped (all ARM instructions IS are conditional). shows the address of the instruction in hexadecimal format, for <instr\_addr> example 00008044. gives the opcode in hexadecimal format, for example e04ec00f. <opcode> <disassembly> gives the disassembly (uppercase if the instruction is taken), for example, SUB r12, r14, pc. This is optional and is enabled by setting Disassemble=True in armul.cnf.

Branches and branches with link in Thumb code appear as two entries, with the first marked:

1st instr of BL pair.

#### **Events (E lines)**

The format of the event (E) lines is as follows:

E <word1> <word2> <event\_number>

For example:

E 00000048 0000000 10005

where:

| <word1></word1>               | gives the first of a pair of words, such as, the pc value.                                                                     |

|-------------------------------|--------------------------------------------------------------------------------------------------------------------------------|

| <word2></word2>               | gives the second of a pair of words, such as, the aborting address.                                                            |

| <event_number></event_number> | gives an event number, for example 0x10005. This is MMU<br>Event_ITLBWalk. Events are described in <i>Events</i> on page 4-91. |

#### 2.3.3 Configuring Tracer

Tracer has its own section in the ARMulator configuration file (armul.cnf):

```

{ Tracer

;; Output options - can be plaintext to file, binary to file or

;; to RDI log window.

;; (Checked in the order RDILog, File, BinFile.)

RDILog=False

File=armul.trc

BinFile=armul.trc

;; Tracer options - what to trace

TraceInstructions=True

TraceMemory=False

TraceIdle=False

TraceNonAccounted=False

TraceEvents=False

;; Where to trace memory - if not set, it will trace at the

;; core.

TraceBus=True

;; Flags - disassemble instructions; start with tracing enabled;

Disassemble=True

StartOn=False

}

```

where:

| RDILog | instructs Tracer to output to the RDI log window (in the GUI debuggers) or the console (under armsd).                               |

|--------|-------------------------------------------------------------------------------------------------------------------------------------|

| File   | defines the file where the trace information is written.<br>Alternatively, you can use BinFile to store data in a binary<br>format. |

The other options control what is being traced:

TraceMemory traces real memory accesses.

TraceIdle traces idle cycles.

TraceNonAccounted

traces unaccounted RDI accesses to memory. That is, those accesses made by the debugger.

- TraceEvents traces events. For more information, see *Tracing events* below.

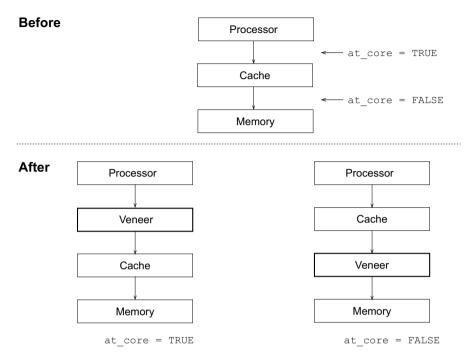

- TraceBus controls the trace data source. This is one of:

TRUE Bus (between processor and memory)

FALSE Core (between core and cache, if present).

For more information, see *ARMul\_InstallMemoryInterface* on page 4-8.

Disassemble disassembles instructions. Simulation is much slower if you enable disassembly.

#### Other tracing controls

You can also control tracing using:

| Range=low addr | ess,high address                                                |

|----------------|-----------------------------------------------------------------|

|                | tracing is carried out only within the specified address range. |

| Sample=n       | only every <i>n</i> th trace entry is sent to the trace file.   |

#### **Tracing events**

When tracing events, you can select the events to be traced using:

```

EventMask=mask,value

```

|              | only those events whose number when masked (bitwise-AND) with <i>mask</i> equals <i>value</i> are traced. |

|--------------|-----------------------------------------------------------------------------------------------------------|

| Event=number | only number is traced. (This is equivalent to EventMask=0xffffffff, number.)                              |

For example, the following traces only MMU/cache events:

EventMask=0xffff0000,0x00010000

See Events on page 4-91 for more information.

#### 2.4 Profiler

Profiler is controlled by the debugger. For more details on Profiler, see Chapter 4 *ARMulator Reference*.

In addition to profiling program execution time, Profiler allows you to use the profiling mechanism to profile events, such as cache misses.

— Note — —

Profiler cannot be used with ARM10 systems. See *Basic ARM ten system* on page 2-31 for information about ARM10 systems.

#### 2.4.1 Configuring Profiler

The Profiler section in the configuration file is as follows:

```

{ Profiler

;; For example - to profile the PC value when cache misses

;; happen, set:

;Type=Event

;Event=0x00010001

;EventWord=pc

}

```

Every line in this section is a comment, so the ARMulator will perform its default profiling. The default is to take profiling samples at intervals of 100 microseconds. Refer to *ADS Debuggers Guide* for further information.

If this section is uncommented, data cache misses will be profiled. See *Events* on page 4-91 for more information.

The Type entry controls how the profiling interval is interpreted:

Type=Microsecond

|            | instructs Profiler to take samples every $n$ microseconds. This is the default.                                             |

|------------|-----------------------------------------------------------------------------------------------------------------------------|

| Type=Cycle | instructs Profiler to take samples every $n$ instructions, and record<br>the number of memory cycles since the last sample. |

| Type=Event | instructs Profiler to ignore the profiling interval. Instead, it profiles relevant events, see <i>Events</i> on page 4-91.  |

EventMask=mask, value is also allowed (see Tracer on page 2-5).

#### 2.5 Pagetable module

On models of ARM architecture v4 processors with a *memory management unit* (MMU), the pagetable module sets up pagetables and initializes the MMU. On processors with a *protection unit* (PU), the pagetable module sets up the PU. To control whether to include the pagetable model, find the UsePageTables tag in the configuration file, armul.cnf, and set it to True or False as appropriate:

```

UsePageTables=True

```

The Pagetables section in armul.cnf controls the contents of the pagetables, and the configuration of the caches and MMU or PU. To locate the Pagetables section, find this line:

```

{ Pagetables

```

For full details of the flags, control register and pagetables described in this section, see the datasheet or technical reference manuals for the processor you are simulating.

#### —— Note ——

This module allows you to benchmark or debug code. You must write ARM code to set up the MMU or PU for a real system.

#### 2.5.1 Controlling the MMU or PU and cache

The first set of flags enables or disables features of the caches and MMU or PU:

```

MMU=Yes

AlignFaults=No

Cache=Yes

WriteBuffer=Yes

Prog32=Yes

Data32=Yes

LateAbort=Yes

BigEnd=No

BranchPredict=Yes

ICache=Yes

HighExceptionVectors=No

FastBus=No

```

Each flag corresponds to a bit in the system control register 1.

Some flags only apply to certain processors. For example, BranchPredict only applies to the ARM810, and ICache to the SA-110 and ARM940T processors. These flags are ignored by other processor models.

The FastBus flag is used by the ARM940T. If your system uses Fast Bus Mode, set FastBus=Yes for benchmarking. If you do not set FastBus, ARMulator assumes that the memory is synchronous with the core. FastBus is set to No by default. You can set it to Yes using the pagetables section of armul.cnf, or a write to CP15.

The MMU flag is also used in processors with a PU.

#### 2.5.2 Controlling registers 2 and 3

The following options apply only to processors with an MMU:

PageTableBase=0xa0000000 DAC=0x00000001

They control:

- the translation table base register (system control register 2)

- the domain access control register (system control register 3).

You must align the address in the translation table base register to a 16KB boundary.

#### 2.5.3 Memory regions

The rest of the Pagetables configuration section defines a set of memory regions. Each region has its own set of properties.

By default, armul.cnf contains a description of a single region covering the whole of the address space:

```

{ Region[0]

VirtualBase=0

PhysicalBase=0

Size=4GB

Cacheable=Yes

Bufferable=Yes

Updateable=Yes

Domain=0

AccessPermissions=3

Translate=Yes

}

```

You can add more regions following the same general form:

| Region[n]    | names the regions, starting with Region[0]. n is an integer.                                                                                                                                                                             |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VirtualBase  | applies only to a processor with an MMU. It gives the address of<br>the base of the region in the virtual address space of the processor.<br>This address must be aligned to a 1MB boundary. It is mapped to<br>PhysicalBase by the MMU. |

| PhysicalBase | gives the physical address of the base of the region. On a processor with an MMU, this address must be aligned to a 1MB boundary.                                                                                                        |

|              | On a processor with a PU it must be aligned to a boundary that is<br>a multiple of the size of the region.                                                                                                                               |

| Size         | specifies the size of this region. On a processor with an MMU<br>Size must be a whole number of megabytes. On a processor with<br>a PU, Size must be 4KB or a power-of-two multiple of 4KB.                                              |

| Cacheable    | specifies whether the region is to be marked as cacheable. If it is, reads from the region will be cached.                                                                                                                               |

| Bufferable   | specifies whether the region is to be marked as bufferable. If it is, writes to the region will use the write buffer.                                                                                                                    |

| Updateable   | applies only to the ARM610 processor. It controls the $\mbox{$U$}$ bit in the translation table entry.                                                                                                                                   |

| Domain          | applies only on processors with an MMU. It specifies the domain field of the table entry.                                                                                                       |

|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AccessPermissio | ons                                                                                                                                                                                             |

|                 | specifies the access controls to the region. Refer to the processor datasheet for further information.                                                                                          |

| Translate       | controls whether accesses to this region cause translation faults.<br>Setting Translate=No for a region causes an abort to occur<br>whenever the processor reads from or writes to that region. |

#### 2.5.4 Pagetable module and memory management units

Processors such as ARM710T and ARM920T have an MMU.

An MMU uses a set of page tables, stored in memory, to define memory regions. On reset, the pagetable module writes out a top-level page table to the address specified in the translation table base register. The table corresponds to the regions you define in the Pagetables section of armul.cnf.

For example, the default configuration details, given in *Memory regions* on page 2-14, define the following page table:

- The entire address space, 4GB, is defined as a single region. This region is cacheable and bufferable. Virtual addresses are mapped directly to the same physical addresses over the whole address space.

- The translation table base register, register 2, is initialized to point to this page table in memory, at 0xa0000000.

- The domain access control register, register 3, is initialized with value 0x00000001. This sets the access to the region as *client*.

- The M, C and W bits of the control register, register 1, are configured to enable the MMU, cache, and write buffer. If the processor has separate instruction and data caches, the I bit configures the instruction cache enabled.

#### 2.5.5 Pagetable module and protection units

Processors such as ARM740T and ARM940T have a PU.

A PU uses a set of protection regions. The base and size of each protection region is stored in registers in the PU. On reset, the page table module initializes the PU.

For example, the default configuration details given above define a single region, region 0. This region is marked as read/write, cacheable, and bufferable. It occupies the whole address range, 0 to 4GB.

#### ARM740T PU

For an ARM740T, the PU is initialized as follows:

- The P, C and W bits are set in the configuration register, register 1, to enable the protection unit, the cache and the write buffer.

- The cacheable register, register 2, is initialized to 1, marking region 0 as cacheable.

- The write buffer control register, register 3, is initialized to 1, marking region 0 as bufferable.

- The protection register, register 5, is initialized to 3, marking region 0 as read/write access.

- The protection region base and size register for region 0 is initialized to 0x3F, marking the size of region 0 as 4GB and marking the region as enabled. The protection region base and size register for region 0 is part of register 6. Register 6 is actually a set of eight registers, each being the protection region base and size register for one region. See the datasheet for the processor for further details.

#### ARM940T PU

For an ARM940T, the PU is initialized as follows:

- The P, D, W, and I bits are set in the configuration register, register 1, to enable the PU, the write buffer, the data cache and the instruction cache.

- Both the cacheable registers, register 2, are initialized to 1, marking region 0 as cacheable for the I and D caches. This is displayed in the debugger as 0x0101, where:

- the low byte (bits 0..7) represent the data cache cacheable register

- the high byte (bits 8..15) represent the instruction cache cacheable register.

- The write buffer control register, register 3, is initialized to 1, marking region 0 as bufferable. This applies only to the data cache. The instruction cache is read only.

- Both the protection registers, register 5, are initialized to 3, marking region 0 as allowing full access for both instruction and data caches. This is displayed in the debugger as 0x00030003, where:

- the low halfword (bits 0..15) represent the data cache protection register

- the high halfword (bits 16..31) represent the instruction cache protection register.

The first register value shown is for region 0, the second for region 1 and so on.

- The protection region base and size register for region 0 is initialized to 0x3F, marking the size of region 0 as 4GB and marking the region as enabled. The protection region base and size register for region 0 is part of register 6. Register 6 is really a set of sixteen registers, each being the protection region base and size register for one region. See the data sheet for the processor for further details.

- Register 7 is a control register. Reading from it is unpredictable. At startup the debugger shows a value of zero. It is not written to by the page table module.

- The programming lockdown registers, register 9, are both initialized to zero. The first register value shown in the debugger is for data lockdown control, the second is for instruction lockdown control.

- The test and debug register, register 15, is initialized to zero. Only bits 2 and 3 have any effect in ARMulator. These control whether the cache replacement algorithm is random or round robin.

#### 2.6 Flat memory model

ARMflat is a model of a zero-wait state memory system. The simulated memory size is not fixed. Host memory is allocated in chunks of 64KB each time a new region of memory is accessed. The memory size is limited by the host computer, but in theory all 4GB of the address space is available. The flat memory model does not generate aborts.

ARMflat is the default memory model used if you do not:

- specify a mapfile or validation model in AXD, ADU, or ADW

- edit armul.cnf.

#### 2.6.1 Selecting the flat memory model

You select the flat model by setting Default=Flat in the Memories section of the armul.cnf file:

{ Memories

;; Default memory model is the "Flat" model, or the "MapFile"

;; model if there is an armsd.map file to load.

; Validation suite uses the trickbox

#if Validate

Default=TrickBox

#endif

;; If there's a memory mapfile, use that.

#if MemConfigToLoad && MEMORY\_MapFile

Default=MapFile

#endif

;; Default default is the flat memory map

Default=Flat

#### 2.7 Fast memory model

ARMfast is a flat memory model of 2MB of RAM. Simulation using ARMfast is typically 17% faster than for ARMflat. This performance increase is partly achieved by not counting cycles, so cycle counts shown by *\$statistics* in the debugger will be zero. This model is intended for use by software developers who want maximum simulation speed, and are not interested in counting cycle or measuring execution time.

The memory size is limited to 2MB. You can change this by editing armfast.c and rebuilding ARMulator, as described in *Rebuilding ARMulator* on page 3-11.

The fast memory model does not generate aborts.

#### 2.7.1 Selecting the fast memory model

You select the fast memory model by setting Default=Fast, in the Memories section of the armul.cnf file:

{ Memories

```

;; Default memory model is the "Flat" model, or the "MapFile"

;; model if there is an armsd.map file to load.

;; Validation suite uses the trickbox

#if Validate

Default=TrickBox

#endif

;; If there's a memory mapfile, use that.

#if MemConfigToLoad && MEMORY_MapFile

Default=MapFile

#endif

;; Default default is the flat memory map

;Default=Flat

Default=Fast

```

#### 2.8 Memory model with memory map

ARMmap is a memory model which you can configure yourself. You can specify the size, access width, access type and access speeds of individual memory blocks in the memory system in a memory map file (see *Map files* on page 4-94).

The debugger internal variables \$memstats and \$statistics give details of accesses of each cycle type, regions of memory accessed and time spent accessing each region.

The map memory model may generate aborts if you specify a memory region with access type as – (hyphen).

#### 2.8.1 Clock frequency

You must specify a simulated clock frequency when using the map memory model. To configure the clock frequency:

- Under armsd, use the command-line option -clock *clockspeed*.

- Under the ADW or ADU, select the **Configure debugger** option from the **Options** menu. In the debugger configuration dialog, click on **Configure** to display the ARMulator configuration dialog. This contains a **Clock Speed** box that you can edit to the required frequency.

- Under AXD, select **Options**  $\rightarrow$  **Configure Target**  $\rightarrow$  **Configure**, enter the required clock speed, and then click the **Emulated** button.

For more information, refer to ADS Debuggers Guide.

The clock frequency is used to determine the number of wait states to be added to each memory access, as well as to calculate time from number of cycles. If you do not specify a clock speed, a value of 1MHz is used.

#### 2.8.2 Selecting the ARMmap memory model

Under armsd, the map memory model is automatically selected as the memory model to use whenever an armsd.map file exists in the directory where armsd is started.

Under the AXD, ADU, or ADW, the map memory model is automatically selected whenever a memory map file is specified. Specify map files using the **Memory Maps** tab of the ARMulator configuration dialog.

```

;; If there's a memory mapfile, use that.

#if MemConfigToLoad && MEMORY_MapFile

Default=MapFile

#endif

```

#### 2.8.3 How the map memory model calculates wait states

The memory map file specifies access times in nanoseconds for nonsequential/sequential reads/writes to various regions of memory. By inserting wait states, the map memory model ensures that every access from the ARM processor takes at least that long.

The number of wait states inserted is the least number required to take the total access time over the number of nanoseconds specified in the memory map file. For example, with a clock speed of 33MHz (a period of 30ns), an access specified to take 70ns in a memory map file results in two wait states being inserted, to lengthen the access to 90ns.

This can lead to inefficiencies in your design. For example, if the access time were 60ns (only 14% faster) the model would insert only one wait state (33% quicker).

A mismatch between processor clock-speed and memory map file can sometimes lead to faster processor speeds having worse performance. For example, a 100MHz processor (10ns period) takes five wait states to access 60ns memory (a total access time of 60ns). At 110MHz, the map memory model must insert six wait states (a total access time of 63ns). So the 100MHz-processor system is faster than the 110MHz processor. (This does not apply to cached processors, where the 110MHz processor would be faster.)

—— Note ———

Access times specified in the memory map file must include propagation delays and memory controller decode time as well as the access time of the memory devices. For example, a map file should specify 80ns for 70ns RAM if there is a 10ns propagation delay.

#### 2.8.4 Configuring the map memory model

You can configure the map memory model to model several different types of memory controller, by editing its entry in the armul.cnf file:

```

{ MapFile

;; Options for the mapfile memory model

CountWaitStates=True

AMBABusCounts=False

SpotISCycles=True

ISTiming=Early

}

```

### **Counting wait states**

By default, the model is configured to count wait states in \$statistics. You can disable this by setting CountWaitStates=False in armul.cnf.

### **Counting AMBA decode cycles**

You can configure the model to insert an extra decode cycle for every nonsequential access from the processor. This models the decode cycle seen on some AMBA bus systems. Enable this by setting AMBABusCounts=True in armul.cnf.

### **Merged I-S cycles**

All ARM processors, particularly cached processors, can perform a nonsequential access as a pair of idle and sequential cycles, known as *merged I-S cycles*. By default, the model treats these cycles as a nonsequential access, inserting wait states on the S-cycle to lengthen it for the nonsequential access.

You can disable this by setting SpotISCycles=False in armul.cnf. However, this is likely to result in exaggerated performance figures, particularly when modeling cached ARM processors.

The model can optimize merged I-S cycles using one of three strategies:

- **Speculative** This models a system where the memory controller hardware speculatively decodes all addresses on idle cycles. The controller can use both the I- and S-cycles to perform the access. This results in one less wait state.

- Early This starts the decode when the ARM declares that the next cycle is going to be an S-cycle, that is, half-way through the I-cycle. This can sometimes result in one fewer wait state. (Whether or not there are fewer wait states depends on the cycle time and the nonsequential access time for that region of memory.)

This is the default setting. You can change this by setting ISTiming=Spec or ISTiming=Late in armul.cnf.

Late This does not start the decode until the S-cycle. In effect all S-cycles that follow an I-cycle are treated as if they are N-cycles.

Refer to the processor datasheet or reference manual for details of merged I-S cycles.

# 2.9 DummyMMU

DummyMMU is a dummy implementation of an ARM architecture v3 or v4 coprocessor 15. It does not provide any of the cache and MMU functions, but does prevent accesses to it being Undefined Instruction exceptions.

Reads from register 0 return a dummy identification register value. You can configure the value to be returned.

Writes to register 1 of the dummy coprocessor (the system configuration register) set the **bigend**, **lateabt** and other signals.

### 2.9.1 Configuring DummyMMU

You can set the code of DummyMMU in the configuration file. Use the following entry in the Coprocessors section of armul.cnf:

```

{ Coprocessors

```

```

; Here is the list of coprocessors, in the form ;; Coprocessor[<n>]=Name

```

```

#if COPROCESSOR_DummyMMU

;; By default, install a dummy MMU on coprocessor 15.

CoProcessor[15]=DummyMMU

```

```

; Here is the configuration for the coprocessors.

;; DummyMMU can be configured to return a given Chip ID

;DummyMMU:ChipID=

#endif

}

```

The line:

```

;DummyMMU:ChipID=

```

can be uncommented and set to any value. For example, to configure DummyMMU to return the ARM710 ID code (0x41017100), change this line to:

```

; Here is the configuration for the coprocessors.

;; DummyMMU can be configured to return a given Chip ID

DummyMMU:ChipID=0x41017100

```

# 2.10 Angel

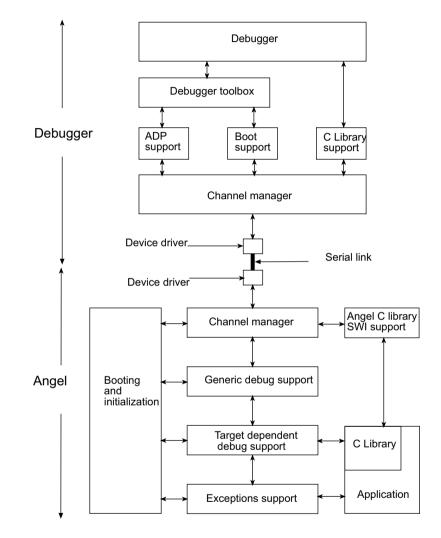

The Angel Debug Monitor is a program which runs on ARM-based hardware. It handles communication between your prototype software, running on the same ARM-based hardware, and a debugger running on your host machine.

When you develop your prototype software on the ARMulator, you can use the Angel operating system model to simulate the Angel Debug Monitor.

### 2.10.1 Configuring Angel

The configuration for the Angel model is in the armul.cnf file. Look for:

```

{ OS

;; Angel configuration

[ ...]

}

```

The configuration options are:

```

AngelSWIARM=0x123456

AngelSWIThumb=0xab

HeapBase=0x40000000

HeapLimit=0x70000000

StackBase=0x80000000

StackLimit=0x70000000

```

where:

AngelSWIARM/AngelSWIThumb

declares the SWI numbers that Angel uses. For descriptions, see Chapter 6 *Semihosting SWIs*.

HeapBase/HeapLimit

defines the application heap.

```

StackBase/StackLimit

```

defines the application stack.

The following options define the initial locations of the exception mode stack pointers.

AddrSuperStack=0xa00 AddrAbortStack=0x800 AddrUndefStack=0x700 AddrIRQStack=0x500 AddrFIQStack=0x400 The semi-hosting C library changes the stack pointer to the value returned by SWI\_SYSHEAPINFO. SWI\_SYSHEAPINFO is set to the value of StackBase configured above. You can specify the location of the User mode stack by editing the address in AddrUserStack:

AddrUserStack=0x80000

These options define the location in memory where ARMulator places the code to handle the hardware exception vectors:

AddrSoftVectors=0xa40 AddrsOfHandlers=0xad0 SoftVectorCode=0xb80

The final option points to a buffer where the Angel model places a copy of the command line. This can be retrieved by catching the RDI\_Info call, RDISet\_Cmdline:

AddrCmdLine=0xf00

The default heap/stack model used by the C library ignores HeapLimit and StackLimit. See the libraries chapter in *ADS Tools Guide* for details.

# 2.11 Peripheral models

ARMulator includes several peripheral models. This section gives basic user information about them. For more detailed information, refer to Chapter 4 *ARMulator Reference*.

\_\_\_\_\_Note \_\_\_\_\_

This section does not apply to ARM10 systems. See *Basic ARM ten system* on page 2-31 for information about peripheral models in ARM10 systems.

### 2.11.1 Configuring ARMulator to use the peripheral models

Enable or disable each peripheral model by changing the relevant entry in the armul.cnf file:

### 2.11.2 Switch

The switch is a model of an address decoder or memory or peripheral controller. It is a configurable address decoder that makes it easier to attach peripheral models without drastically reducing the performance of ARMulator.

The switch is a veneer between the processor core and memory. It routes memory accesses to the appropriate memory model. Routing is based on the access address and a set of memory address ranges, peripheral address ranges, and peripheral address masks.

The switch is installed if any of the reference peripheral models is enabled.

### 2.11.3 Interrupt controller

In addition to IntCEnabled, the interrupt controller has the following configuration items:

```

{ InterruptController

Range=0x0a000000,0x0a00010c

;; set WARN to enable warnings about invalid register accesses

WARN=FALSE

WAITS=1

}

```

Range specifies the area in memory into which the interrupt controller registers are mapped. For details of the interrupt controller registers, see *Interrupt controller* on page 4-121.

WAITS specifies the number of wait states that accessing the interrupt controller imposes on the processor. The maximum is 30.

### 2.11.4 Timer

In addition to TimerEnabled, the timer has the following configuration items:

```

{ TimerCounter

Range=0x0a800000,0x0a80003f

;; The RPS Clock. This is usually the processor clock rate

CLK=20000000

;; Interrupt controller source bits - 4 and 5 as standard

IntOne=4

IntTwo=5

;; set WARN to enable warnings about invalid register accesses

WARN=FALSE

WAITS=1

}

```

Range specifies the area in memory into which the timer registers are mapped. For details of the interrupt controller registers, see *Timer* on page 4-123.

CLK is used to specify the clock rate of the peripheral. This is usually the same as the processor clock rate.

IntOne specifies the interrupt line connection to the interrupt controller for timer 1 interrupts. IntTwo specifies the interrupt line connection to the interrupt controller for timer 2 interrupts.

WAITS specifies the number of wait states that accessing the timer imposes on the processor. The maximum is 30.

### 2.11.5 Watchdog

Use Watchdog to prevent a failure in your program locking up your system. Watchdog resets ARMulator if your program fails to access it before a predetermined time.

— Note –

ARM do not supply a hardware watchdog timer. This is a generic model of a watchdog timer. It is supplied to help users model their system environment.

In addition to WDogEnabled, Watchdog has the following configuration items:

```

{ WatchDog

Range=0xb000000,0xb000004

KeyValue=0x12345678

WatchPeriod=0x80000

IRQPeriod=3000

IntNumber=16

StartOnReset=True

RunAfterBark=True

;; set WARN to enable warnings about invalid register accesses

WARN=FALSE

WAITS=1

}

```

Range specifies the area in memory into which the watchdog registers are mapped.

This is a two-timer watchdog.

If StartOnReset is True, the first timer starts on reset. If StartOnReset is False, the first timer starts only when your program writes the configured key value to the KeyValue register.

The first timer generates an **IRQ** after WatchPeriod memory cycles, and starts the second timer. The second timer times out after IRQPeriod memory cycles, if your program has not written the configured key value to the KeyValue register. Configure IRQPeriod to a suitable value to allow your program to react to the **IRQ**.

If RunAfterBark is True, Watchdog halts ARMulator if the second timer times out. You can continue to execute, or debug.

If RunAfterBark is False, Watchdog resets ARMulator and halts.

IntNumber specifies the interrupt line number that Watchdog is attached to.

WAITS specifies the number of wait states that accessing the watchdog imposes on the processor. The maximum is 30.

# 2.12 Other models

This section gives basic user information about the less complex models. For more detailed information, refer to Chapter 4 *ARMulator Reference*.

—— Note ———

This section does not apply to ARM10 systems. See *Basic ARM ten system* on page 2-31 for information about peripheral models in ARM10 systems.

### 2.12.1 Stack tracker

The stack tracker examines the contents of the stack pointer (r13) after each instruction. It keeps a record of the lowest value and from this it can work out the maximum size of the stack. ARMulator runs more slowly with stack tracking enabled.

To enable the stack tracker, edit armul.cnf.

1. Find the line:

TrackStack=False

2. Change it to:

TrackStack=True

Before initialization the stack pointer may contain values outside the stack limits. You must configure the stack limits so that the stack tracker can ignore values outside them.

```

;; The StackUse model continually monitors the stack pointer and

;; reports the amount of stack used in $statistics. It needs to

;; be configured with the stack's location.

{ StackUse

StackBase=0x80000000

StackLimit=0x70000000

}

```

StackBase is the address of the top of the stack. StackLimit is a lower limit for the stack. Changing these values does not reposition the stack in memory. To reposition the stack, you must reconfigure the Angel model (see *Configuring Angel* on page 2-24).

### 2.12.2 Windows Hourglass

This model calls the debugger regularly during execution. This is required when you are using AXD, ADU or ADW. If you want to alter the interval between calls to the debugger, find the section listed below in armul.cnf and edit it.

```

{ WindowsHourglass

;; We can control how regularly we callback the frontend

;; More often (lower value) means a slower simulator, but

;; faster response. The default is 8192.

Rate=8192

}

```

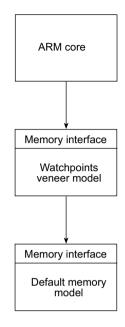

### 2.12.3 Watchpoints

Watchpoints provides memory watchpoints. It is a veneer between the processor core and memory, or cache as appropriate.

To enable watchpoints, change the WatchpointsEnabled line in armul.cnf:

;; To enable watchpoints, set "WatchPointsEnabled" WatchpointsEnabled=True

Disable watchpoints when benchmarking code. Enable watchpoints when debugging code using watchpoints.

### 2.12.4 Validate

This is a small coprocessor that is used to validate the behavior of the ARM simulator. It can cause interrupts and busy-waits, for example.

### 2.12.5 Trickbox

This is a memory model of a system where accessing various addresses causes events, such as aborts and interrupts.

### 2.12.6 Bytelane

This is a veneer memory model. It is a veneer between the processor and the real memory model. It converts accesses from the core into byte-lane accesses. Byte-lane accesses are also known as byte-strobe accesses.

### 2.12.7 ARM PIE

This is a model of the ARM PIE card. It is only available for UNIX.

# 2.13 Basic ARM ten system

*Basic ARM Ten System* (BATS) is a separate modelling scheme from ARMulator. You cannot use any of the other ARMulator models, such as Profiler or Tracer, with BATS.

To use BATS:

- 1. Select BATS instead of ARMulator as your debugger target.

- 2. Select a *configuration trace file* (CTR file) from your debugger interface.

- 3. Either:

- specify the name of your chosen CTR file when you start armsd

- select the name of a CTR file from the list in the BATS configuration window in AXD, ADU, or ADW.

See ADS Debuggers Guide for details.

### 2.13.1 Configuration trace files

CTR files describe the configurations of the systems that BATS can model. They describe which components are used by the system and how they are interconnected. Some components have configuration options which are specified in the CTR file.

Three CTR files are supplied with BATS. See:

- *ARM1020T* on page 2-32

- ARM1020T\_PERIP on page 2-33

- *ARMv5TM* on page 2-35.

You can also write your own CTR files. You can do this by copying one of the supplied files and editing the copy. See *Basic ARM ten system configuration trace files* on page 4-114 for more information.

In all the supplied configurations:

- the heap occupies 0x30000000 to 0x70000000 of the address space

- the stack occupies 0x80000000 to 0x70000000 of the address space

- the time resolution is 10ps.

### 2.13.2 ARM1020T

The ARM1020T configuration trace file, ARM1020T.ctr, defines a model of an ARM1020T system with two memory modules. It has:

- a system coprocessor (cp15)

- a memory management unit

- a write buffer

- separate instruction and data caches.

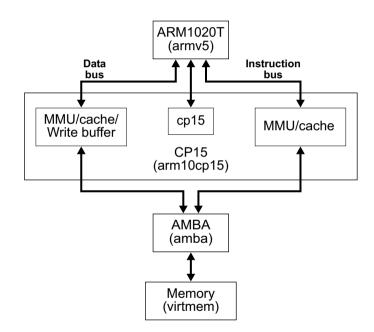

Communication between the caches or write buffer and the external memory modules is through the AMBA bus. This system is shown in Figure 2-1. The filenames of BATS modules are shown in brackets. For further information see *Creating instances* on page 4-115.

Figure 2-1 ARM1020T system

### 2.13.3 ARM1020T\_PERIP

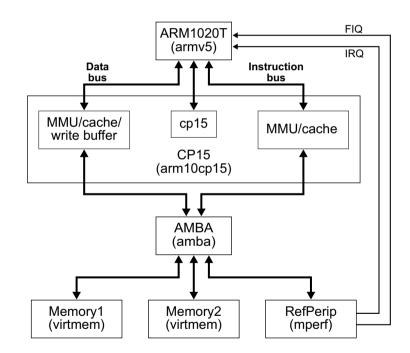

The ARM1020T\_PERIP configuration trace file, ARM1020T\_PERIP.ctr, defines a model of an ARM1020T system with two memory modules and a set of reference peripherals. It has:

- a system coprocessor (cp15)

- a memory management unit

- a write buffer

- separate instruction and data caches.

Communication between the caches or write buffer and the external memory modules is through the AMBA bus. This system is shown in Figure 2-2. The filenames of BATS modules are shown in brackets. For further information see *Creating instances* on page 4-115.

Figure 2-2 ARM1020T\_PERIP system

### **Reference peripherals**

The following facilities of the reference peripherals are implemented:

- *Interrupt controller* on page 4-121.

- *Timer* on page 4-123.

See Reference Peripherals Specification for additional details.

### ARM1020T\_PERIP memory map

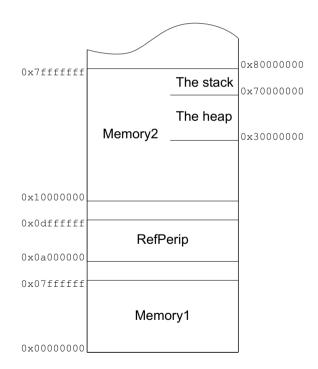

In ARM1020T\_PERIP, as shown in Figure 2-3:

- Memoryl occupies 0x00000000 to 0x07ffffff of the address space

- the reference peripherals occupy 0x0a000000 to 0x0dffffff of the address space

- Memory2 occupies 0x10000000 to 0x7fffffff of the address space.

### Figure 2-3 Memory map of ARM1020T\_PERIP

### 2.13.4 ARMv5TM

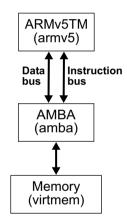

The ARMv5TM configuration trace file, ARMv5TM.ctr, defines a model of a generic ARM architecture v5 system with one memory module. It has no coprocessor 15 or caches.

\_\_\_\_\_Note \_\_\_\_\_

This model does not correspond to any real hardware. It cannot be used for benchmarking. It is supplied for software development and debugging purposes only.

Although hardware without caches would be slower if it existed, the simulation is faster without the caches.

This system is shown in Figure 2-4. The filenames of BATS modules are shown in brackets. For further information see *Creating instances* on page 4-115.

Figure 2-4 ARMv5TM system

ARMulator Basics

# Chapter 3 Writing ARMulator Models

This chapter is intended to assist you in writing your own models to add to ARMulator. It contains the following sections:

- Adding models to ARMulator on page 3-2

- Writing a new peripheral model on page 3-6

- Writing a new cache model on page 3-7

- Rebuilding ARMulator on page 3-11

- *Configuring ARMulator to use the example* on page 3-15.

# 3.1 Adding models to ARMulator

This chapter does not contain information about the *Basic ARM Ten System* (BATS). For information about BATS, see *Basic ARM ten system* on page 2-31.

You can add extra models to ARMulator without altering the existing models. Each model is self-contained, and communicates with ARMulator through defined interfaces. The definition of these interfaces is in Chapter 4 *ARMulator Reference*.

The source code of some models can be found in the rebuild kit on UNIX in:

Install\_Directory\ARMulate

or on PC in:

Install\_Directory\ARMulate\Win32\ARMulate\user

Use these files as examples to help you write your own models. To help you choose suitable models to examine, this chapter includes a list of them with brief descriptions of what they do (see *Supplied models* on page 3-4).

You can make a copy of one of these models and edit the copy.

To use your new model, you must rebuild ARMulator using the appropriate compiler (see *Rebuilding ARMulator* on page 3-11).

### 3.1.1 Model stubs

Basic models, memory models, coprocessor models, and operating system models attach to ARMulator through a stub. A stub consists of an initialization function and a textual name for the model. ARMulator uses the textual name to locate the initialization function.

Basic models can be initialized either before or after memory models are initialized. This means that there are two distinct types of basic model:

- early models

- late models.

ARMulator locates each model in turn, calling the initialization function of each model, and passing in a pointer to a structure containing a list of pointers.

Each model fills in this set of function pointers at initialization time. The model should also register an ExitUpcall() (see *ExitUpcall* on page 4-55) during initialization, to free any memory that it allocates.

### Model initialization sequence

The model initialization functions are called in the following order:

- 1. ARMulator core model

- 2. Early basic models, such as peripheral models (see *Basic model interface* on page 4-4)

- 3. Memory models, including veneer memory models installed by an early basic model (see *Basic model interface* on page 4-4)

- 4. Coprocessor models

- 5. Operating system models

- 6. Late basic models (see *Basic model interface* on page 4-4).

### 3.1.2 Supplied models

ARMulator is supplied with source code for the following groups of models:

- Basic models

- Peripheral models

- Memory models on page 3-5

- *Coprocessor models* on page 3-5

- *Operating system models* on page 3-5.

### **Basic models**

| tracer.c   | The tracer module can trace instruction execution and events from within ARMulator (see <i>Tracer</i> on page 4-89). You can link your own tracing code onto the tracer module, allowing real-time tracing for example. tracer is an early basic model.                                                                                                                  |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| profiler.c | The profiler module provides the profiling function (see <i>Profiler</i> on page 2-11). This includes basic instruction sampling and more advanced use, such as profiling cache misses. It does this by providing an UnkRDIInfoHandler that handles the profiling requests from the debugger (see <i>UnkRDIInfoUpcall</i> on page 4-62). profiler is a late basic model. |

| pagetab.c  | On reset, this module sets up cache, PU or MMU and associated pagetables inside ARMulator (see <i>Pagetable module</i> on page 2-12). pagetab is a late basic model.                                                                                                                                                                                                     |

| stackuse.c | If enabled this model tracks the stack size. Stack usage is reported<br>in the ARMulator memory statistics. You can set the stack upper<br>and lower bounds in the armul.cnf file.stackuse is a late basic<br>model.                                                                                                                                                     |

### **Peripheral models**

All the peripheral models are early basic models.

intc.c See Interrupt controller on page 2-27. intc is a model of the interrupt controller peripheral described in the Reference Peripherals Specification (RPS).

timer.c See Timer on page 2-27. timer is a model of the RPS timer peripheral. Two timers are provided. timer must be used in conjunction with an interrupt controller, but not necessarily intc.

| watchdog.c | Watchdog. See <i>Watchdog</i> on page 2-28. watchdog is a generic |

|------------|-------------------------------------------------------------------|

|            | watchdog model. It does not model any specific watchdog           |

|            | hardware, but provides generic watchdog functions.                |

### Memory models

The following source files are provided for memory models:

| armflat.c | This module implements a flat model of 4GB RAM.                                                                                                                                                                                                             |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| armfast.c | This module implements a flat model of 2MB RAM.                                                                                                                                                                                                             |

| armmap.c  | This memory model allows you to specify memory layout using<br>an armsd.map file, see <i>Map files</i> on page 4-94. This slows down<br>simulation speed, so when no armsd.map file is present,<br>ARMulator uses the faster armflat.c model in preference. |

| excache.c | excache is an example of a basic cache model. See <i>Writing a new cache model</i> on page 3-7. excache provides a starting point for you to write your own cache models.                                                                                   |

| tracer.c  | As well as being a basic model, the tracer module provides a veneer memory model that can log memory accesses.                                                                                                                                              |

### **Coprocessor models**

| dummymmu.c | This is a cut-down model of coprocessor 15 (the system |

|------------|--------------------------------------------------------|

|            | coprocessor).                                          |

### Operating system models

| angel.c | This is an implementation of the <i>Software Interrupts</i> (SWIs) and<br>environment required for running programs linked with the<br>semihosted C library on ARMulator. |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| noos.c  | This is a dummy operating system model, where no SWIs are intercepted.                                                                                                    |

# 3.2 Writing a new peripheral model

A peripheral model is an early model that is accessed via the switch memory model. The switch model carries out partial address decoding to select a memory device. An address range or an address mask is specified in the armul.cnf file for the switch to control which peripherals are accessed for an address.

A template file, called template.c, is provided in the user directory of the rebuild kit. There is a companion file called notes.txt. notes.txt is a step by step guide that explains how to write a peripheral model based on the supplied template.

# 3.3 Writing a new cache model

A cache memory model is a veneer between the processor model and the main memory model. Other veneer memory models, for which the source code is supplied, can be used as examples to help you write your own model. One example is watchpnt.c. Both the MMUlator and the StrongMMU cache simulators are part of the core ARMulator, and are not supplied in source form.

Memory models have two main parts:

- *Initialization* on page 3-8

- *Memory access* on page 3-10.

An example cache model, excache.c, is supplied in the ARMulator rebuild kit.

The file excache.c defines an extra memory model. For ARMulator to know about this model, you must declare the model in models.h by adding the line:

MEMORY(ExampleCache)

The reference ExampleMemory comes from ARMul\_MemStub ExampleCache in the file example.c.

You must also add the object file to the supplied Makefile, along with a rule for building the model.

### 3.3.1 Initialization

A cache model must include the standard initialization functions, such as allocating a state, setting up the interface and so on. It must also:

- Use ToolConf\_Lookup(config, ARMulCnf\_Memory) to find the name of the memory model.